Called Spectre FX Simulator, it is the next generation of the company’s ‘FastSpice’ branded products, aimed at pre and post-layout verification of large DRAM, flash, SRAM and transistor-level SoC designs.

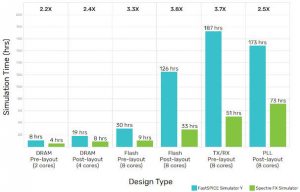

“Design teams can verify functionality, timing for sign-off in a productive manner,” according to the company. “Spectre FX Simulator delivers up to 3x transient simulation performance with equivalent or superior accuracy over the latest FastSpice simulators and the ability to leverage up to 32 parallel CPU cores.” (see histogram). Techniques are implemented to “handle

both sensitive analogue circuits and event-driven digital circuits in the same design.”

The new simulator is built on the same infrastructure technology, and has been added to, Cadence’ Spectre Simulation Platform for what it describes as “a complete analogue simulation solution between the various verification tasks from cell characterisation through chip-level verification”.

FX Simulator relies on Spectre platform’s technologies including parsing, device models and Verilog-A, and has its own built-in SPICE solver. “This means that, for most FastSpice verification applications, designers can use the default mode to get accuracy with fast enough simulation speed,” said Cadence.

“Several tens of millions of RC parasitics” can be handled, said the company, and it supports post-layout simulation with DSPF, SPEF and extracted SPICE formats.

The parasitics file can be a flat or a hierarchical netlist included directly in the main net list or can be back-annotated into a pre-layout net list to ease debugging.

The product page is here