The Versal AI Edge chipsets have been designed to meet the compute densities demanded by AI-enabled automated systems for real-time control. They have 10 times the compute density of the Zynq UltraScale+ MPSoCs for low latency, intelligent, autonomous systems and support IEC 61508, DO-254/178 and ISA 26262 safety standards for industrial, avionics and automotive applications.

“Edge computing applications require an architecture that can evolve to address new requirements and scenarios with a blend of flexible compute processing within tight thermal and latency constraints,” said Sumit Shah, senior director, product management and marketing at Xilinx.

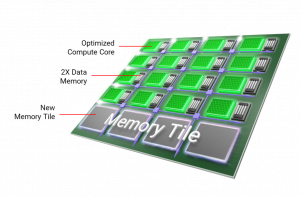

The Versal AI Edge series is based on the 7nm Versal architecture, miniaturised for AI compute at low latency and down to 6W operation. There are scalar engines for embedded compute, adaptable engines for sensor fusion and hardware adaptability, and intelligent engines for AI inference that scales up to 479 (INT4) TOPS. Xilinx says this figure is “unmatched by ASSPs and GPUs targeting edge applications”. The compute performance is also suited to advanced signal processing workloads for vision, radar, lidar, and software defined radio.

For connectivity there are LPDDR-4266, 32Gbit/s transceivers, 40G multi-rate Ethernet, PCIe Gen4 with CCIX, and native MIPI support for vision sensors up to 8Mpixels.

Development tools include Vivado for hardware developers, the Vitis unified software platform for software developers, Vitis AI for data scientists, and domain-specific operating systems, frameworks, and acceleration libraries for target applications.

Design documentation and support for the latest members of the ACAP portfolio are available now to early access customers. Shipments are expected to begin in the first half of 2022. The company will publish a roadmap for automotive- and defence-grade devices then.