Farnell الأسهم OrangeCrab FPGA مجلس التنمية

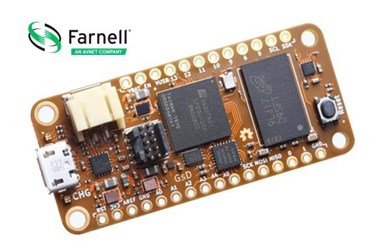

قامت Farnell بتوسيع نطاق مجموعات تطوير أجهزة الكمبيوتر أحادية اللوحة (SBC) مع إضافة لوحة تطوير FPGA مفتوحة المصدر OrangeCrab r0.2 من Good Stuff Department.

Good Stuff Department هو مطور لمنتجات الأجهزة مفتوحة المصدر مع التركيز على وحدات التحكم الصغيرة ولوحات تطوير FPGA.

يجمع OrangeCrab بين عامل شكل Adafruit Feather المضغوط للغاية والقوة العالية التي ترتبط عادةً بلوحات تطوير مصفوفات البوابة القابلة للبرمجة الميدانية (FPGA) الأكبر حجمًا.

يعتمد OrangeCrab على Lattice EPC5 FPGA ويتميز بتكوينين للذاكرة بما في ذلك ECP5 25F / 128Mbit و ECP5 85F / 521Mbit. يتوافق FPGA مع سلسلة الأدوات مفتوحة المصدر ويمكن استخدامه لتجربة RISC-V وأنظمة SoCs الأخرى. مجموعة الأجهزة الطرفية المضمنة في OrangeCrab تجعلها مناسبة للعديد من تطبيقات العالم الحقيقي.

يمكن للمستخدمين الانتقال عبر CircuitPython إلى OrangeCrab القادرة على استضافة المترجم الفوري. على الرغم من عدم تنفيذها حاليًا ، إلا أن المطورين يتمتعون أيضًا بحرية استهداف FPGA نفسها باستخدام برنامج HDL المُصنَّع بواسطة برنامج gateware. للمهندسين الأكثر دراية بمنصة التطوير على مستوى SoC ، يمكن لـ ECP5 تشغيل برنامج RISC-V softcore. كما يوفر مشروع LiteX للمطورين مزيدًا من المرونة والقدرة ..

وتعليقًا على هذا الإعلان ، قال رومان سورو ، رئيس SBC في Farnell ، "إن لوحة تطوير FPGA مفتوحة المصدر والمزودة بميزات متعددة الاستخدامات من OrangeCrab تعد إضافة رائعة إلى مجموعتنا الواسعة من لوحات تطوير SBC ومجموعات التقييم. إن OrangeCrab عبارة عن لوحة مصممة بمهارة ومتعددة الاستخدامات يمكن استخدامها لمجموعة من التطبيقات الاحترافية - أو بواسطة هواة مهتمين بشدة بأجهزة FPGA ".

تشمل الميزات الرئيسية للوحة تطوير OrangeCrab r0.2 FPGA ما يلي:

- المعالج: شعرية أشباه الموصلات EPC5 FPGA مع عناصر LUT 24K ورأس برمجة FPGA ذو 10 سنون ومقبس MicroSD مع اتصال USB مباشر كامل السرعة بـ FPGA.

- ذاكرة: تتضمن خيارات الذاكرة ذاكرة نظام تصل إلى 8 جيجابت DDR3 (x16) وتخزين 128 أو 512 ميجابت ذاكرة فلاش QSPI. أ بطاقة μSD الفتحة تزيد من إمكانات التخزين بلوحة التطوير.

- شكل عامل: يتبع OrangeCrab مواصفات لوح الريش النحيف من Adafruit بأبعاد 22.86 مم × 50.8 مم فقط. إنه صغير بما يكفي ليتم حمله في الجيب أثناء العمل كأرضية كاملة للنماذج الأولية لتصميمات SoC المخصصة.

- الربط: يتيح محمل إقلاع USB مفتوح المصدر للمستخدمين الاتصال عبر واجهة USB الأصلية الخاصة بـ FPGA لتحميل الكود والوصول إلى الذكريات عبر MSD. يعتبر الرأس القياسي 2 × 5 ، 1.27 مم إضافة رائعة لأولئك الذين يتطلعون إلى تطوير التطبيقات على طبقة USB.

- الطاقة: تقدم DCDC عالي الكفاءة للإمدادات الرئيسية ، شريحة شاحن بطارية (100 مللي أمبير) ، موصل بطارية LiPo (نوع PH) ومذبذب 48 ميجا هرتز.