벡터 유닛은 여러 계산을 병렬로 수행하는 여러 벡터 코어로 구성됩니다.

이 경우 Semidynamics의 벡터 코어는 요구 사항에 따라 FP64, FP32, FP16, BF16, INT64, INT32, INT16 또는 INT8 데이터 유형을 지원하도록 맞춤화할 수 있습니다. 구현된 가장 긴 워드 길이는 벡터 코어 폭('ELEN')을 정의합니다. .

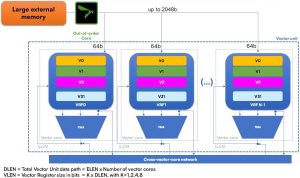

벡터 유닛은 4, 8, 16 또는 32개의 코어를 가질 수 있으며 총 벡터 유닛 데이터 경로 폭('DLEN' = ELEN x 코어 수)은 128비트에서 2,048비트 사이일 수 있습니다.

벡터 장치 내에서 최대 32개의 벡터 코어를 연결할 수 있는 올-투-올 교차 벡터 코어 네트워크를 사용할 수 있습니다. Semidynamics에 따르면 "교차 벡터 코어 장치는 vrgather 및 vslide와 같은 서로 다른 벡터 코어 간에 데이터를 섞는 RISC-V 표준의 특정 명령에 사용됩니다."

벡터 단위 내에서 각 벡터 레지스터(VLEN)의 비트 수는 '1x'(VLEN=DLEN)를 넘어 2x, 4x 또는 8x로 조정할 수 있습니다. VLEN이 DLEN보다 크면 벡터 작업이 여러 사이클을 사용하여 실행됩니다. “예를 들어, VLEN=2,048 및 DLEN=512인 경우 각 벡터 산술 연산을 실행하는 데 4클럭이 걸립니다. 이것은 큰 메모리 대기 시간을 허용하고 전력을 줄이기 위한 훌륭한 기능입니다.”

세미다이내믹스 CEO는 "우리의 기술은 함께 RISC-V를 새로운 수준으로 끌어올리고 현재 사용 가능한 가장 빠른 빅 데이터 처리를 통해 비디오 처리, AI 및 머신 러닝과 같은 고성능 컴퓨팅 응용 분야에서 기회를 열 것"이라고 말했습니다. 창립자 Roger Espasa.

벡터 장치는 비순차적이며 Semidynamics의 비순차적 Atrevido 64비트 RISC-V 코어와 쌍을 이룹니다. 주문형 코어가 파이프라인에 있으며 회사는 고객의 지적 재산과 일치하는 특수 인터페이스와 프로토콜을 제공할 수 있습니다.

Semidynamics는 2016년에 설립되었으며 스페인 바르셀로나에 본사를 두고 있으며 맞춤형 RISC-V 프로세서 IP를 제공하며 기계 학습 및 AI용 벡터 장치가 있는 고성능 코어를 전문으로 합니다. 개인 소유이며 RISC-V Alliance의 회원입니다.

RISC-V Summit Europe이 5년 9월 2023일부터 6일까지 바르셀로나에서 개최됩니다. 스탠드 XNUMX에서 Semidynamics를 찾아보세요.