Ornamentum quod spectat in elemento logico 481,000 RTPF 500 FPGA, quod includit 33Mbit of sram, 1,480 stipites DSP et 24 vicos transceptivarum 10Gbit/s in 1,509 clavum ceramicum.

FPGA in tabulis sunt prototypi (magis quam spatii gradus) partes, et sunt actu quattuor ornamenta, electionem CB1509 vel CG1509 praebentes involucrum, et "STD" vel "-1" gradus velocitatis.

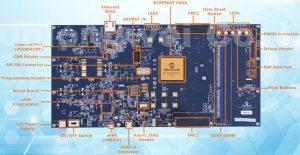

"RtPF tabulae progressionis", ut nota sunt, duos HPC FMC connexiones pro schedulis filialibus, DDR3 x72 DIMM connexiones memoriae, Gigabit Ethernet, a CAN bus header, et USB-UART connexum, et 1Gbyte SPI mico.

"Est programmator FlashPro6 in tabula infixa programmandi per USB-JTAG programmandi sine programmate externo", secundum comitatum. "Designatores, qui programmate externo uti malunt, ut FlashPro6, accessum habent ad JTAG programmandi caput in tabula."

Inclusa etiam est radiorum notitia, et instrumentum programmandi ad programmatum Libero, licet: "A Libero SoC Design Software Platinum licentia uti oportet artificio RTPF500T, quod mercandum est et cum ornamento non continetur", dixit Microchip.

In arca e regione tabulae sunt 12V 5A potentia adaptor, funis Aer, USB 2.0 micro A ad Mini-B iungo pro interface UART et card velocem initium.

Societas eas videt adhibitas esse ad altitudinem celeritatis transceiveri aestimationem, potestatem, DSP, communicationes algorithms vel imaginum processus algorithms.

FPGA evolutionis radiophonicus ornamentum productum paginae hic inveniri potest