Pada prinsipnya, IC melaksanakan pengganda kapasitans litar untuk mencontohi Y-Kapasitor dalam reka bentuk penapis pasif konvensional.

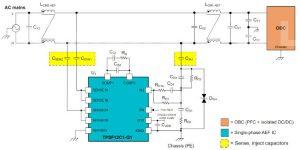

Mereka lakukan semasa duduk di antara induktor dan kapasitor penapis yang lebih kecil (gambarajah atas) sambil menjumlahkan komponen frekuensi tinggi voltan daripada dua atau empat konduktor kuasa ac, dan kemudian menyuntik arus ac anti-fasa yang diperoleh daripada isyarat ini kembali ke dalam neutral.

"Kapasitans aktif yang berkesan ditetapkan oleh keuntungan litar dan kapasitansi suntikan," menurut TI. “Penderiaan penapis EMC aktif dan impedans suntikan menggunakan nilai kapasitans yang agak rendah dengan komponen kecil

jejak kaki.”

[Tatal ke bawah ke bahagian bawah artikel ini untuk perbincangan tentang di mana betul-betul arus mengalir dalam skema ini]

Kapasitor deria dan suntikan (lihat gambar rajah) mestilah komponen berkadar Y.

Komponen pasif lain pada output adalah untuk redaman - untuk menguruskan resonans antara kearuhan pencekik mod biasa yang masih diperlukan dan kapasitansi suntikan - yang muncul dalam perolehan gelung aktif sebagai sepasang sifar kompleks.

Terdapat empat peranti: TPSF12C1 dan TPSF12C3 untuk aplikasi komersial satu dan tiga fasa, kemudian TPSF12C1-Q1 dan TPSF12C3-Q1 untuk kegunaan automotif. Pengeluaran volum dijadualkan pada suku kedua 2023, dengan IC penapis EMI aktif tambahan muncul akhir tahun ini.

Operasi melebihi 8 hingga 16V (18V tahan) dan lebih tinggi 105°C ambien (150°C simpang).

Perlindungan termasuk di bawah-voltan penguncian, dan penutupan haba, dan terdapat pad daya.

Mereka "memenuhi keperluan imuniti lonjakan IEC 61000-4-5, meminimumkan keperluan untuk komponen perlindungan luaran seperti diod penindasan voltan sementara", kata TI.

Pembungkusan ialah 4.2 x 3.3mm 14pad SOT-23

Aplikasi diramalkan dalam pengecas on-board, pelayan dan bekalan kuasa yang tidak terganggu.

Nota permohonan ini mempunyai maklumat paling jelas tentang IC ini dan termasuk contoh Peraruh pengurangan saiz

Mingguan Elektronik memikirkan cara skim ini berfungsi (Sila baca tindak balas TI dengan segera di bawah ini, dengan mengatakan bahawa pertimbangan ini adalah salah, walaupun tidak menjelaskan di mana gelung arus yang disuntik berada. Sekiranya ia adalah masalah tatanama, soalan lanjut telah dihantar mengenai gelung semasa yang dikaitkan dengan arus yang disuntik) .

Pertimbangan EW:

Kesusasteraan TI banyak menyebut menyuntik arus ke dalam talian neutral, tetapi tidak, nampaknya Electronics Weekly, bahawa terminal tanah (dan Vdd+decoupling) bagi IC sedang melakukan sebahagian besar kerja. Tanah IC disambungkan ke tanah EMC, dan tenaga EMC mod biasa dibuang melalui sini, sama seperti dengan kapasitor Y biasa - tetapi keuntungan dalam litar mengurangkan yang diperlukan kapasitor saiz.

Kapasitor Y dalam reka bentuk pasif digantikan dengan keuntungan tambah CNJI dan laluan melalui kapasitor X sedia ada - sebenarnya, IC dan litarnya telah menukar beberapa hingar mod biasa kepada bunyi berbeza yang boleh ditangani oleh kapasitor X. Dalam sistem tiga fasa tanpa neutral, CNJI perlu diganti dengan bintang tiga kapasitor.

Soalan EW: Adakah bunyi mod biasa dikeluarkan dengan menyuntik arus ac ke dalam tanah melalui pin sambungan tanah IC?

Tindak balas TI: Tidak, arus AC disuntik ke dalam talian kuasa yang sama dalam amplitud tetapi bertentangan dalam fasa untuk membatalkan hingar CM.

Soalan EW: Jika ya, dan jika arus ini adalah relatif kepada garis neutral: Adakah litar ini menukarkan beberapa hingar mod biasa yang ditindas kepada hingar berbeza – yang masih terdapat pada talian kuasa bukan neutral (atau talian, dalam tiga fasa )

Tindak balas TI: Tidak, hingar CM tidak ditukar kepada hingar DM. Bunyi DM mungkin masih wujud dalam talian kuasa, tetapi hingar CM dikurangkan secara khusus oleh AEF. Bunyi CM mendominasi pada frekuensi yang lebih rendah melalui sumbangan kapasitansi parasit sistem dan bertanggungjawab terutamanya untuk saiz penapis yang besar.