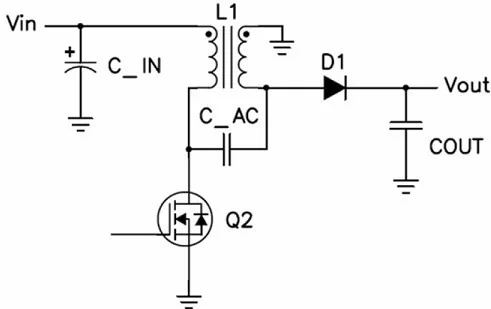

Figura 1 O conversor SEPIC usa uma chave para aumentar e diminuir a tensão de saída

As formas de onda de corrente e tensão deste circuito são semelhantes aos circuitos reversos de modo de corrente contínua (CCM). Quando Q1 é ligado, ele utiliza a tensão de entrada do estágio principal do indutor acoplado para formar energia no circuito.

Quando Q1 é desligado, a tensão do indutor inverte e é então fixada na tensão de saída. O capacitor C_AC é a diferença entre o SEPIC e o circuito reverso; quando Q1 é ligado, a corrente do indutor secundário flui através dele e então aterra. Quando Q1 está desligado, a corrente do indutor primário flui através de C_AC, aumentando assim a corrente de saída que flui através de D1.

Comparado com o circuito reverso, uma grande vantagem desta topologia é que as tensões do FET e do diodo são fixadas por C_AC e há muito pouco toque no circuito. Desta forma, podemos optar por utilizar uma tensão mais baixa, e assim produzir um dispositivo de maior eficiência.

Como esta topologia é semelhante à topologia reversa, muitas pessoas pensariam que é necessário um conjunto de enrolamentos fortemente acoplados. No entanto, este não é o caso. A Figura 2 mostra os dois estados operacionais do SEPIC contínuo, o transformador foi modelado por indutância de dispersão (LL), indutância de magnetização (LM) e um transformador ideal (T).

Após a inspeção, a tensão da indutância de fuga é igual à tensão de C_AC. Portanto, um pequeno valor de C_AC ou uma grande tensão CA com uma pequena indutância de fuga formará uma grande corrente de loop. Correntes de loop maiores reduzirão a eficiência e o desempenho EMI do conversor, e esta situação é indesejável. Uma maneira de reduzir esta grande corrente de loop é aumentar o capacitor de acoplamento (C_AC).

No entanto, isso tem o custo de custo, tamanho e confiabilidade. Um método mais astuto é aumentar a indutância de vazamento, o que pode ser facilmente alcançado quando um componente magnético personalizado é especificado.

2a) mosfet está ligado: VLL = VC_AC -VIN = ∆VC_AC(A parte DC é excluída)

2b) MOSFET desligado: VLL = VIN + VOUT -VC_AC -VOUT = ∆VC_AC (Parte DC excluída)

Figura 2a e 2b conversor SEPIC em dois estados de funcionamento.

A tensão CA da indutância de fuga é igual à tensão do capacitor de acoplamento.

Curiosamente, poucos fabricantes perceberam esse fato e muitos fabricantes produziram indutores de baixa indutância de vazamento para aplicações SEPIC.

Por outro lado, a Coilcraft possui um MSD47 de 1260 uH com uma indutância de vazamento de cerca de 0.5 uH. Ao mesmo tempo, também desenvolveu recentemente outras versões deste projeto, que possui uma indutância de fuga superior a 10 uH. Será apresentado em “, então fique ligado.