นักวิจัยจากมหาวิทยาลัยร็อคกี้เฟลเลอร์ได้เปิดโลกทัศน์ใหม่เกี่ยวกับกฎของมัวร์—อาจเป็นการทำนายทางเทคโนโลยีที่มีชื่อเสียงที่สุดในโลก—ความหนาแน่นของชิปหรือจำนวนส่วนประกอบในวงจรรวมจะเพิ่มเป็นสองเท่าทุกสองปี

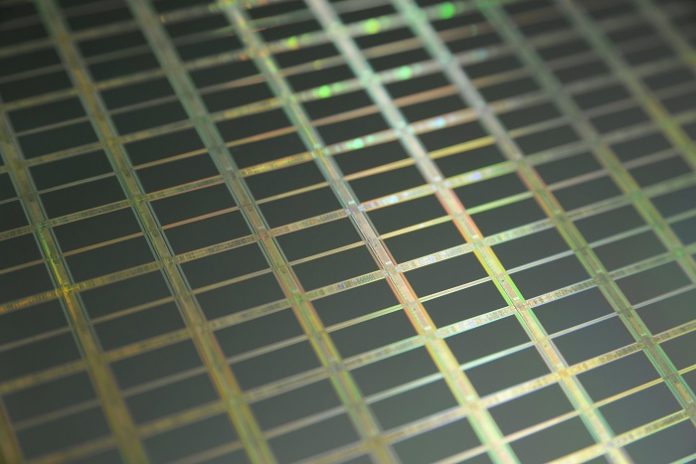

การศึกษาเผยให้เห็นรูปแบบคลื่นทางประวัติศาสตร์ที่เหมาะสมยิ่งขึ้นในการเพิ่มขึ้นของ ทรานซิสเตอร์ ความหนาแน่นของชิปซิลิกอนที่ทำให้คอมพิวเตอร์และอุปกรณ์ไฮเทคอื่นๆ เร็วขึ้นและมีประสิทธิภาพมากขึ้น

อันที่จริง ตั้งแต่ปีพ.ศ. 1959 ได้มีการปรับปรุงดังกล่าวมาแล้ว XNUMX ระลอก โดยแต่ละครั้งกินเวลาประมาณหกปี ในระหว่างนั้น ทรานซิสเตอร์ ความหนาแน่นต่อชิปเพิ่มขึ้นอย่างน้อย 10 เท่า กฎของมัวร์กลับมาอีกครั้งผ่านความหนาแน่นของชิป Intel งานใหม่นี้ทำให้ความโค้งของรูปแบบคลื่นชัดเจนขึ้นโดยการนำมุมมองใหม่เกี่ยวกับความหนาแน่นของชิป โดยคำนึงถึงขนาดที่เปลี่ยนแปลงของชิปที่ใช้ใน Fairchild สารกึ่งตัวนำ โปรเซสเซอร์ระหว่างประเทศและ Intel เริ่มต้นในปี 1959

ผู้เขียน Jesse Ausubel และ David Burg จาก Program for the Human Environment (PHE) แห่งมหาวิทยาลัยร็อคกี้เฟลเลอร์ นิวยอร์ก กล่าวว่า หลังจากช่วงคลื่นการเติบโตหกปีแต่ละช่วง จะมีการเติบโตเพียงเล็กน้อยประมาณสามปีตามมา

การเติบโตครั้งต่อไปในการย่อขนาดทรานซิสเตอร์และความสามารถในการคำนวณนั้นเกินกำหนดแล้ว

และจะถูกดึงโดยความต้องการเช่นเทคโนโลยีปัญญาประดิษฐ์ที่หิวกระหายข้อมูลเช่นการจดจำใบหน้าเครือข่ายเซลลูล่าร์และอุปกรณ์ 5G รถยนต์ที่ขับด้วยตนเองและนวัตกรรมไฮเทคที่คล้ายกันซึ่งต้องการความเร็วในการประมวลผลและความสามารถในการประมวลผลที่มากขึ้น

บริษัทสตาร์ทอัพ Cerebras ได้ขนานนามชิปที่ใหญ่ที่สุดเท่าที่เคยสร้างมา นั่นคือ Wafer-Scale Engine ซึ่งใหญ่กว่าหน่วยประมวลผลกราฟิก (GPU) ที่ใหญ่ที่สุด 56 เท่า ซึ่งครองแพลตฟอร์มการประมวลผลสำหรับ AI และการเรียนรู้ของเครื่อง

“ชิปขนาดเวเฟอร์มีทรานซิสเตอร์ 1.2 ล้านล้านตัว ฝังคอร์ที่ปรับให้เหมาะสม AI 400,000 คอร์ (มากกว่า GPU ที่ใหญ่ที่สุด 78 เท่า) และมีหน่วยความจำบนชิปมากกว่า 3,000 เท่า”

อย่างไรก็ตาม การสิ้นสุดของยุคชิปซิลิกอนอยู่ในมุมมอง โดยเหลือเพียงพัลส์ซิลิกอนเพียงหนึ่งหรือสองครั้งก่อนที่ความก้าวหน้าต่อไปจะยากขึ้นแบบทวีคูณเนื่องจากความเป็นจริงทางกายภาพและข้อ จำกัด ทางเศรษฐกิจ

การเติบโตอย่างต่อเนื่องของอุตสาหกรรมคอมพิวเตอร์จะขึ้นอยู่กับนวัตกรรมที่ย่อขนาด เช่น นาโนทรานซิสเตอร์ ทรานซิสเตอร์แบบอะตอมเดี่ยว และการคำนวณควอนตัม

ในปี 2019 บริษัทแม่ของ Google Alphabet อ้างว่ามีความก้าวหน้าในการคำนวณควอนตัมด้วยโปรเซสเซอร์ซูเปอร์คอมพิวเตอร์ที่ตั้งโปรแกรมได้ชื่อ "Sycamore" โดยใช้คิวบิตตัวนำยิ่งยวดที่ตั้งโปรแกรมได้

“ตัวอย่างการเปรียบเทียบที่เผยแพร่รายงานว่าในเวลาประมาณ 200 วินาที Sycamore ทำงานเสร็จซึ่งจะใช้ซูเปอร์คอมพิวเตอร์ที่ล้ำสมัยในปัจจุบันประมาณ 10,000 ปี”

Mr Ausubel ผู้อำนวยการ PHE กล่าวว่า "เราได้ปีนขึ้นไปถึงหกครั้งในหุบเขาที่สูงขึ้นของซิลิคอนและพื้นผิวที่คล้ายคลึงกัน แต่อาจออกจากหุบเขาซิลิกอนเพื่อชมทิวทัศน์ของวัสดุและกระบวนการอื่นๆ"

“สวน Qubit อาจรออยู่ในตอนท้ายของการปีนป่ายในปัจจุบัน”

อย่างไรก็ตาม การวิเคราะห์ความหนาแน่นของทรานซิสเตอร์เผยให้เห็นรูปแบบการเติบโตของคลื่นอนุกรมของการเติบโตที่ซับซ้อนมากขึ้น โดยแต่ละเฟสของเทคโนโลยีจะกินเวลารวมทั้งสิ้นประมาณเก้าปีก่อนที่จะอิ่มตัวและแทนที่ด้วยเฟสใหม่

งานนี้ใช้แบบจำลองที่พัฒนาขึ้นเพื่อศึกษาการเติบโตโดยมีการป้อนกลับที่ซับซ้อนซึ่งนำไปสู่ข้อจำกัดด้านความหนาแน่นที่เคยใช้ในการวิจัยดังกล่าว เขาเสริม และแสดงพลังของพวกมันในการทำให้เห็นวิวัฒนาการที่ซับซ้อนของเครื่องจักรที่หลากหลาย

ELE ไทม์ส

-

ELE ไทม์สhttps://www.eletimes.com/author/eletimes-newsFPGA ระดับกลางบรรลุความสำเร็จครั้งถัดไปสำหรับระบบ Edge Compute

-

ELE ไทม์สhttps://www.eletimes.com/author/eletimes-newsห้องสมุดดิจิทัลที่กำลังเติบโตของ Mouser นำเสนอข้อมูลเชิงลึกของผู้เชี่ยวชาญเกี่ยวกับเทคโนโลยีและแอพพลิเคชั่นที่เป็นนวัตกรรมในปัจจุบัน

-

ELE ไทม์สhttps://www.eletimes.com/author/eletimes-newsรายงานภัยคุกคามทางไซเบอร์ของ SonicWall ปี 2021: การโจมตีด้วยแรนซัมแวร์ 304.7 ล้านครั้งในเวลาเพียง 6 เดือน

-

ELE ไทม์สhttps://www.eletimes.com/author/eletimes-newsAcies และ Jackstien ประกาศการร่วมทุนเพื่อสร้างแอปพลิเคชั่นที่ทันสมัยบน Revolutio