Compact development board encourages FPGA experimentation

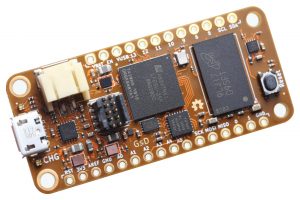

It is based on the Lattice EPC5-FPGA with QSPI flash memory – depending on the choice of EPC5-25F (128-Mbit) or ECP5-85F (512-Mbit) – and up to 8-Gbit DDR3 of on-board system memory.

The FPGA is compatible with the open-source toolchain and can be used with RISC-V and other soft core SoCs. Users can port over CircuitPython to the OrangeCrab which can be host the interpreter and developers can target the FPGA with gateware synthesised HDL.

The EPC5 FPGAs have 24k LUT elements and 10-pin programming headers. There is a Micro SD socket for additional storage, if required, which has full speed direct USB connection to the FPGA. The FPGAs can also run a RISC-V soft core.

The open-source USB bootloader enables users to connect over the FPGA’s native USB interface to upload code and access the memories over MicroSD. The standard 2×5, 1.27mm header can be used to develop applications on the USB layer.

The SBC has high power efficiency for mains supply operation, says Farnell, with a 100mA battery charger chip, a LiPo battery connector (PH type) and a 48-MHz oscillator.