ケイデンスが最新のAWRデザイン環境プラットフォームを発表

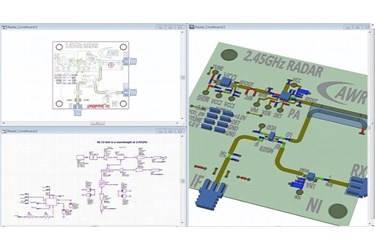

Cadence Design Systemsは、RFからミリ波への知的財産(RF IP)統合をサポートするクロスプラットフォームの相互運用性を提供するAWR Design Environmentバージョン16(V16)を発表しました。

異種混合を対象としています テクノロジー Cadence Virtuoso 設計プラットフォームだけでなく、Allegro PCB および IC パッケージ設計プラットフォーム全体にわたる開発も可能です。

V16リリースでは、Clarity 3DSolverおよびCelsiusThermal Solverとのシームレスな統合が導入され、大規模で複雑なRFシステムの電熱性能分析に無制限の容量を提供します。 Microwave Office回路設計ソフトウェアを含むAWR設計環境は、顧客が自動車、レーダーシステム、および 半導体 テクノロジー。 ケイデンスによると、V16リリースでのプラットフォームとソルバーの統合により、競合するワークフローと比較して、ターンアラウンドタイム(TAT)が最大50%短縮されます。

「競争の激しい5G /ワイヤレス市場で今日勝つために、顧客は、チップで開始および停止するだけでなく、システム全体に拡張する完全で包括的なRFワークフローを可能にするソリューションを求めています」とコーポレートバイスプレジデントのVinodKariatは述べています。ケイデンスでの研究開発の「AWRDesignEnvironment V16リリースによって可能になったRFワークフローの革新は、設計データとソフトウェアIPが製品間で共有され、シームレスに転送される方法の根本的な進歩から始まります。 包括的なケイデンスの傘の下で、このリリースで導入されたRF統合のレベルは、エンジニアリングチームの生産性の真の進歩です。」

プラットフォームの相互運用性は、RF統合を加速し、エンジニアリングの生産性を促進するために不可欠です。AWR設計環境、Virtuoso、およびAllegroプラットフォーム間で設計データをシームレスに共有することにより、RF設計チームと製造レイアウトチームの間の切断を排除し、エンジニアリングリソースを節約し、積極的に使用できるようになりました。開発スケジュールに影響を与えます。

V16リリースとそのディープ電磁(EM)および熱埋め込み分析により、お客様はTATが3分のXNUMX以上削減されていることを確認しています。