“AI is driving tremendous needs for higher data throughput in data centres and lower power consumption,” said Sevalia. A Bloomberg report predicted that the AI data centre market will reach $200bn by 2027. Rapid upgrade cycles for AI hardware will be essential to running data and compute-intensive AI workloads, observed SiTime.

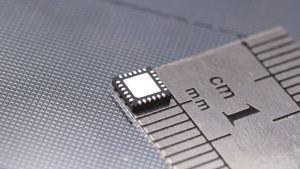

The ClkSoC integrates the MEMS resonator in a 4x4mm QFN plastic package to address the limitations of legacy clock generators and matching the resonator’s impedance with the clock, said the company. It also saves hardware designers having to compensate for any performance comprises through the use of discrete products such as clocks, oscillators and resonators in a design.

Replacing up to four standalone oscillators can reduce the board area for timing by up to 50% in data centre equipment such as servers, switches, acceleration cards and smart network interface cards (NICs).

The SiT91211 and Si91213 clock generators (150fs, supporting 400GHz Ethernet and 70fs phase jitter model) are sampling now to strategic customers and general availability is expected in the second half of this year.