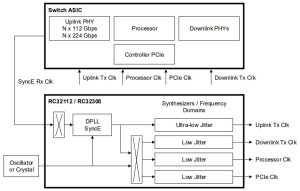

RC32312 and RC32308 “provide phase noise and jitter required to meet the needs of 112Gbit/s as well as 224Gbit/s SerDes designs using commonly-available 48MHz to 73MHz crystals”, claimed the company. “The devices can generate up to four frequency domains and offer integrated low-drop regulators with superior power supply rejection.”

Clocks are available with 50fs rms jitter (12kHz to 20MHz) supporting SerDes up to 112Gbit/s, and 25fs rms (same range, with 4MHz high pass filter) supporting 224Gbit/s SerDes.

RC32312 has four differential clock inputs and 12 differential clock outputs.

RC32308 has three differential clock inputs and eight differential clock outputs.

Both provide a digital PLL (phase-locked loop) and an ultra-low phase noise analog PLL for clock synthesisis, and three fractional output

divider (FOD) based clock synthesisers.

The differential clock inputs can each be configured as two single-ended inputs, operating up to 1GHz differential or 250MHz single-ended.

The differential outputs can be configured for 1GHz LVDS or HCSL, or as two 250MHz LVCMOS outputs.

A frequency reference is required – a crystal connected to two of the pads, or an externally-generated signal.

Phase noise, frequency accuracy and frequency stability of the outputs depend on this reference, although the analogue PLL synthesises reduces phase noise on its output, producing “virtually any frequency between 9.7 and 10.75GHz”, said Renesas.

The rest of the signal generators use this sanitised clock.

“The FODs are capable of integer division, rational division [M/N] and fractional division with 1 part per trillion frequency resolution,” said Renesas.

Two power rails are needed, one at 1.8V and one at 3.3V. Consumption is over a watt and operation is over -40 to +85°C (125°C junction max).

Packaging is 7 x 7mm 48pad VFQFPN or 9 x 9mm 64pad VFQFPN.

The parts are compliant with ITU-T G.8262 and G.8262.1 for enhanced synchronous Ethernet, according to Renesas, which expects use with Ethernet PHYs up to 1.6Tbit/s.

Find the RC323xx product page here