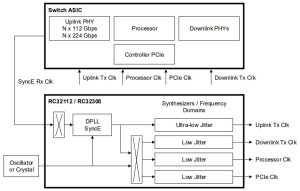

Les RC32312 et RC32308 « fournissent le bruit de phase et la gigue nécessaires pour répondre aux besoins des conceptions SerDes à 112 Gbit/s ainsi qu'à 224 Gbit/s en utilisant des cristaux couramment disponibles de 48 MHz à 73 MHz », a affirmé la société. « Les appareils peuvent générer jusqu'à quatre domaines de fréquence et offrir des régulateurs intégrés à faible chute avec un rejet d'alimentation supérieur. »

Les horloges sont disponibles avec une gigue de 50 fs rms (12 kHz à 20 MHz) prenant en charge des SerDes jusqu'à 112 Gbit/s, et 25 fs rms (même plage, avec filtre passe-haut de 4 MHz) prenant en charge des SerDes de 224 Gbit/s.

Le RC32312 dispose de quatre entrées d'horloge différentielle et de 12 sorties d'horloge différentielle.

Le RC32308 dispose de trois entrées d'horloge différentielle et de huit sorties d'horloge différentielle.

Les deux fournissent une PLL numérique (boucle à verrouillage de phase) et une PLL analogique à bruit de phase ultra faible pour la synthèse d'horloge, ainsi que trois sorties fractionnaires.

synthétiseurs d'horloge basés sur un diviseur (FOD).

Les entrées d'horloge différentielle peuvent chacune être configurées comme deux entrées asymétriques, fonctionnant jusqu'à 1 GHz différentiel ou 250 MHz asymétrique.

Les sorties différentielles peuvent être configurées pour LVDS ou HCSL 1 GHz, ou comme deux sorties LVCMOS 250 MHz.

Une référence de fréquence est requise – un cristal connecté à deux des pastilles ou un signal généré en externe.

Le bruit de phase, la précision de la fréquence et la stabilité de la fréquence des sorties dépendent de cette référence, bien que les synthèses analogiques PLL réduisent le bruit de phase sur sa sortie, produisant « pratiquement n'importe quelle fréquence entre 9.7 et 10.75 GHz », a déclaré Renesas.

Le reste des générateurs de signaux utilisent cette horloge aseptisée.

"Les FOD sont capables de division entière, de division rationnelle [M/N] et de division fractionnaire avec une résolution de fréquence de 1 partie par billion", a déclaré Renesas.

Deux rails d'alimentation sont nécessaires, un à 1.8 V et un à 3.3 V. La consommation est supérieure à un watt et le fonctionnement est supérieur à -40 à +85°C (jonction 125°C max).

L'emballage est 7 x 7 mm 48pad VFQFPN ou 9 x 9 mm 64pad VFQFPN.

Les composants sont conformes aux normes ITU-T G.8262 et G.8262.1 pour l'Ethernet synchrone amélioré, selon Renesas, qui prévoit une utilisation avec des PHY Ethernet jusqu'à 1.6 Tbit/s.

Retrouvez la page produit du RC323xx ici