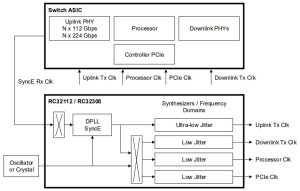

RC32312 및 RC32308은 "일반적으로 사용 가능한 112MHz ~ 224MHz 크리스털을 사용하여 48Gbit/s 및 73Gbit/s SerDes 설계의 요구 사항을 충족하는 데 필요한 위상 잡음 및 지터를 제공합니다"라고 회사는 주장했습니다. "이 장치는 최대 XNUMX개의 주파수 도메인을 생성할 수 있으며 뛰어난 전원 공급 제거 기능을 갖춘 통합 저드롭 레귤레이터를 제공합니다."

클록은 최대 50Gbit/s의 SerDes를 지원하는 12fs rms 지터(20kHz~112MHz)와 25Gbit/s SerDes를 지원하는 4fs rms(동일 범위, 224MHz 고역 통과 필터 포함)로 제공됩니다.

RC32312에는 12개의 차동 클록 입력과 XNUMX개의 차동 클록 출력이 있습니다.

RC32308에는 XNUMX개의 차동 클록 입력과 XNUMX개의 차동 클록 출력이 있습니다.

둘 다 클록 합성을 위한 디지털 PLL(위상 고정 루프) 및 초저 위상 잡음 아날로그 PLL과 3개의 분수 출력을 제공합니다.

분배기(FOD) 기반 클록 합성기.

차동 클록 입력은 각각 1개의 단일 종단 입력으로 구성될 수 있으며 최대 250GHz 차동 또는 XNUMXMHz 단일 종단으로 작동합니다.

차동 출력은 1GHz LVDS 또는 HCSL용으로 구성하거나 250개의 XNUMXMHz LVCMOS 출력으로 구성할 수 있습니다.

주파수 기준이 필요합니다(두 개의 패드에 연결된 크리스탈 또는 외부에서 생성된 신호).

출력의 위상 잡음, 주파수 정확도 및 주파수 안정성은 이 레퍼런스에 따라 달라지지만 아날로그 PLL 합성은 출력의 위상 잡음을 줄여 "9.7~10.75GHz 사이의 거의 모든 주파수"를 생성한다고 Renesas는 말했습니다.

나머지 신호 발생기는 이 정리된 클럭을 사용합니다.

“FOD는 1조당 XNUMX파트 주파수 분해능으로 정수 나누기, 유리수 나누기(M/N) 및 분수 나누기가 가능합니다.”라고 Renesas는 말했습니다.

1.8개의 전원 레일이 필요합니다. 하나는 3.3V, 다른 하나는 40V입니다. 소비량은 85와트 이상이며 작동 온도는 -125~+XNUMX°C(접합점 최대 XNUMX°C)입니다.

포장은 7 x 7mm 48패드 VFQFPN 또는 9 x 9mm 64패드 VFQFPN입니다.

Renesas에 따르면 이 부품은 향상된 동기식 이더넷을 위한 ITU-T G.8262 및 G.8262.1을 준수하며 최대 1.6Tbit/s의 이더넷 PHY와 함께 사용할 것으로 예상됩니다.

여기에서 RC323xx 제품 페이지를 찾아보세요.