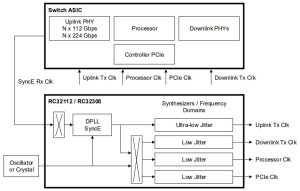

RC32312 und RC32308 „liefern Phasenrauschen und Jitter, die erforderlich sind, um die Anforderungen von 112-Gbit/s- sowie 224-Gbit/s-SerDes-Designs unter Verwendung allgemein verfügbarer 48-MHz- bis 73-MHz-Quarze zu erfüllen“, behauptete das Unternehmen. „Die Geräte können bis zu vier Frequenzbereiche erzeugen und bieten integrierte Low-Drop-Regler mit hervorragender Stromversorgungsunterdrückung.“

Takte sind mit 50fs RMS-Jitter (12kHz bis 20MHz) erhältlich, die SerDes bis zu 112Gbit/s unterstützen, und 25fs RMS (gleicher Bereich, mit 4MHz-Hochpassfilter) und unterstützen 224Gbit/s SerDes.

RC32312 verfügt über vier differenzielle Takteingänge und 12 differenzielle Taktausgänge.

RC32308 verfügt über drei differenzielle Takteingänge und acht differenzielle Taktausgänge.

Beide verfügen über eine digitale PLL (Phase-Locked-Loop) und eine analoge PLL mit extrem geringem Phasenrauschen für die Taktsynthese sowie drei fraktionierte Ausgänge

Clock-Synthesizer auf Basis eines Teilers (FOD).

Die differenziellen Takteingänge können jeweils als zwei Single-Ended-Eingänge konfiguriert werden und mit bis zu 1 GHz Differential oder 250 MHz Single-Ended betrieben werden.

Die Differenzausgänge können für 1 GHz LVDS oder HCSL oder als zwei 250 MHz LVCMOS-Ausgänge konfiguriert werden.

Es ist eine Frequenzreferenz erforderlich – ein Quarz, der an zwei der Pads angeschlossen ist, oder ein extern erzeugtes Signal.

Phasenrauschen, Frequenzgenauigkeit und Frequenzstabilität der Ausgänge hängen von dieser Referenz ab, obwohl die analoge PLL-Synthese das Phasenrauschen an ihrem Ausgang reduziert und „praktisch jede Frequenz zwischen 9.7 und 10.75 GHz“ erzeugt, sagte Renesas.

Die übrigen Signalgeneratoren verwenden diesen bereinigten Takt.

„Die FODs sind in der Lage, ganzzahlige Divisionen, rationale Divisionen [M/N] und gebrochene Divisionen mit einer Frequenzauflösung von 1 Teil pro Billion durchzuführen“, sagte Renesas.

Es werden zwei Stromschienen benötigt, eine mit 1.8 V und eine mit 3.3 V. Der Verbrauch liegt bei über einem Watt und der Betrieb liegt bei über -40 bis +85 °C (maximal 125 °C Anschlussstelle).

Die Verpackung besteht aus 7 x 7 mm 48pad VFQFPN oder 9 x 9 mm 64pad VFQFPN.

Die Teile entsprechen ITU-T G.8262 und G.8262.1 für erweitertes synchrones Ethernet, so Renesas, das eine Verwendung mit Ethernet-PHYs mit bis zu 1.6 Tbit/s erwartet.

Die RC323xx-Produktseite finden Sie hier