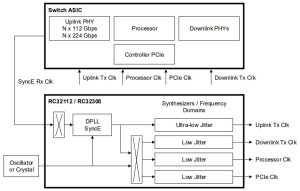

RC32312とRC32308は「一般的に入手可能な112MHz~224MHzのクリスタルを使用して、48Gbit/sおよび73Gbit/sのSerDes設計のニーズを満たすのに必要な位相ノイズとジッターを提供する」と同社は主張している。 「このデバイスは最大 XNUMX つの周波数ドメインを生成でき、優れた電源除去を備えた統合型低ドロップ レギュレーターを提供します。」

クロックは、最大 50Gbit/s の SerDes をサポートする 12fs rms ジッター (20kHz ~ 112MHz)、および 25Gbit/s SerDes をサポートする 4fs rms (同じ範囲、224MHz ハイパス フィルター付き) で利用できます。

RC32312 には 12 つの差動クロック入力と XNUMX の差動クロック出力があります。

RC32308 には XNUMX つの差動クロック入力と XNUMX つの差動クロック出力があります。

どちらも、クロック合成用のデジタル PLL (フェーズ ロック ループ) と超低位相ノイズ アナログ PLL、および 3 つのフラクショナル出力を提供します。

分周器 (FOD) ベースのクロック シンセサイザー。

差動クロック入力はそれぞれ 1 つのシングルエンド入力として構成でき、最大 250GHz の差動または XNUMXMHz のシングルエンドで動作します。

差動出力は、1GHz LVDS または HCSL 用に、または 250 つの XNUMXMHz LVCMOS 出力として構成できます。

周波数基準、つまり 2 つのパッドに接続された水晶振動子、または外部生成信号が必要です。

出力の位相ノイズ、周波数精度、および周波数安定性はこの基準に依存しますが、アナログ PLL 合成により出力の位相ノイズが低減され、「9.7 ~ 10.75 GHz の実質的にすべての周波数」が生成されるとルネサスは述べています。

残りの信号発生器は、このサニタイズされたクロックを使用します。

「FODは、1兆分のXNUMXの周波数分解能で、整数除算、有理除算[M/N]、および分数除算が可能です」とルネサスは述べています。

1.8 つの電源レールが必要で、3.3 つは 40 V、もう 85 つは 125 V です。消費電力は XNUMX ワットを超え、動作温度は -XNUMX ~ +XNUMX °C (接合部最大 XNUMX °C) です。

パッケージは 7 x 7mm 48pad VFQFPN または 9 x 9mm 64pad VFQFPN です。

ルネサスによれば、この部品は拡張同期イーサネット用の ITU-T G.8262 および G.8262.1 に準拠しており、最大 1.6Tbit/s のイーサネット PHY での使用が想定されています。

RC323xx 製品ページはこちら