パナソニックが新たに開発 半導体 基板材料

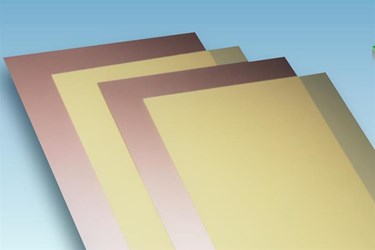

パナソニックは、インダストリアルソリューションズ社が製品化したと発表した。 半導体 パッケージの低反り性と高信頼性を両立したパッケージ基板材料(品番:R-1515V)です。

この材料は、パッケージングプロセス中の基板の反りを低減する非常に低い熱膨張特性と、リフローアセンブリ中に作成されるはんだ接合部の残留応力を低減するように設計された最適化された機械的特性を備えています。 材料の量産は2021年XNUMX月に開始される予定です。

パナソニックによると、現世代の高度なパッケージ設計は、比較的大きなフットプリント、多数のI / O、および2.5Dパッケージに見られるような高密度の相互接続構造を示し、動作性能の向上とともに、ほとんどの産業および商用アプリケーションが要求します。組み立てられたパッケージからの高い組み立てレベルの信頼性。

パナソニックは、パッケージ基板を含む、マザーボード材料および半導体のパッケージングとアセンブリ用の幅広い製品を開発してきました。 カプセル化材料; アセンブリレベルの補強材とその専門知識を活用することにより、反りが少なく、アセンブリレベルの信頼性が高い新しい半導体基板材料を配合しました。

チップパッケージングの信頼性を向上させるには、パッケージング中の基板の反りを減らす必要があります。 IC 基板とそれに続くカプセル化プロセス。 さらに、半導体パッケージをマザーボードに組み立てるリフロー組み立てプロセス中にはんだボールにかかる応力も、長期的な動作の信頼性を確保するために下げる必要がありました。

パナソニックによると、この新しい基板材料の熱膨張係数(CTE)は、シリコンICチップの熱膨張係数(CTE)にはるかに近い(同社が測定した場合は4 ppm)。 パッケージングプロセス中に発生する熱エクスカーションによって引き起こされる反りを低減します。 さらに、新しい基板材料は、大幅に改善された厚さ公差を特徴とし、基板とICチップ間の安定した接合を保証し、パッケージ化されたチップの信頼性をさらに向上させます。 新しい材料の変更された柔軟性とバッファリング特性により、はんだボールへのストレスが軽減され、アセンブリレベルの信頼性が向上します。