„Unsere Netzwerksynchronisationsplattform ZL3073x/63x/64x implementiert Mess-, Kalibrierungs- und Abstimmungsfunktionen, wodurch der Zeitfehler der Netzwerkausrüstung erheblich reduziert wird, um die strengsten 5G-Anforderungen zu erfüllen“, sagte Rami Kanama, Vice President of Timing Components des Unternehmens, der sie als „flexibel“ beschreibt Architektur zur Implementierung der notwendigen Kanaldichte sowie Low-Jitter-Synthesizer helfen beim Design von Timing Cards, Linecards, Radio Units [RUs], Centralized Units [CUs] und Distributed Units [DUs] für 5G-Funkzugangsnetze [RANs] .“

Das Unternehmen behauptet, den ITU-T-Standard G.8273.2 Klasse C 30 ns max.

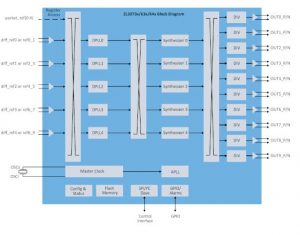

Bis zu fünf unabhängige DPLL-Kanäle (Digital Phase Locked Loop) stehen für eine Verlustleistung von 900 mW aus einem 9 x 9 mm Gehäuse zur Verfügung. Jitter wird mit 100fs rms angegeben.

Andere Teile der Netzwerksynchronisationsplattform sind der lizenzierbare ZLS30730-Algorithmus und Microchips ZLS30390 IEEE 1588-2008 Protocol Engine für Precision Time Protocol (PTP) und Clock Recovery. OX-601 OCXO (Ovenised Crystal Oscillator) ist ein weiterer Bestandteil im Portfolio des Unternehmens.

Zu den Entwicklungstools gehören eine grafische Benutzeroberfläche, ein Evaluierungsboard und Anwendungshinweise.