"La nostra piattaforma di sincronizzazione di rete ZL3073x/63x/64x implementa capacità di misurazione, calibrazione e regolazione, riducendo significativamente l'errore di tempo delle apparecchiature di rete per soddisfare i più severi requisiti 5G", ha affermato il vicepresidente dell'azienda dei componenti di temporizzazione Rami Kanama, che lo descrive come "un flessibile architettura per implementare la necessaria densità di canale, così come sintetizzatori a basso jitter aiutano la progettazione di schede di temporizzazione, schede di linea, unità radio [RU], unità centralizzate [CU] e unità distribuite [DU] per reti di accesso radio 5G [RAN] .”

L'azienda afferma di soddisfare gli standard ITU-T G.8273.2 Classe C 30 ns max e l'emergente classe D (5 ns max) requisiti di errore temporale.

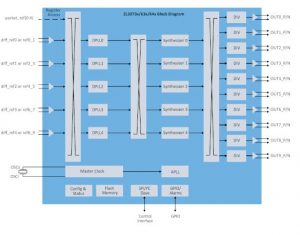

Sono disponibili fino a cinque canali DPLL (digital phase-locked loop) indipendenti per una dissipazione di 900 mW da un contenitore da 9 x 9 mm. Si dice che il jitter sia 100fs rms.

Altre parti della piattaforma di sincronizzazione di rete sono l'algoritmo ZLS30730 concesso in licenza e il motore di protocollo ZLS30390 IEEE 1588-2008 di Microchip per il protocollo PTP (Precision Time Protocol) e il ripristino dell'orologio. OX-601 OCXO (oscillatore a cristalli forni) è un'altra parte del portafoglio dell'azienda.

Gli strumenti di sviluppo includono un'interfaccia utente grafica, una scheda di valutazione e note applicative.