“Nossa plataforma de sincronização de rede ZL3073x / 63x / 64x implementa recursos de medição, calibração e ajuste, reduzindo significativamente o erro de tempo do equipamento de rede para atender aos requisitos 5G mais rigorosos”, disse o vice-presidente de componentes de temporização da empresa Rami Kanama, que o descreve como “um sistema flexível arquitetura para implementar a densidade de canal necessária, bem como sintetizadores de baixo jitter ajudam no projeto de cartões de tempo, placas de linha, unidades de rádio [RUs], unidades centralizadas [CUs] e unidades distribuídas [DUs] para redes de acesso de rádio 5G [RANs] . ”

A empresa está alegando que atingiu o padrão ITU-T G.8273.2 Classe C 30ns máximo e os requisitos de erro de tempo emergentes Classe D (5ns máximo).

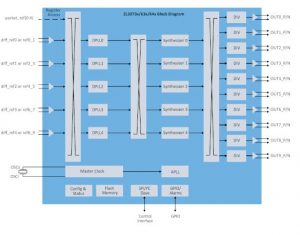

Até cinco canais DPLL (loop digital de bloqueio de fase) independentes estão disponíveis para uma dissipação de 900mW em um pacote de 9 x 9 mm. Jitter é afirmado como 100 ffs rms.

Outras partes da plataforma de sincronização de rede são o algoritmo ZLS30730 licenciável e o mecanismo de protocolo ZLS30390 IEEE 1588-2008 da Microchip para protocolo de tempo de precisão (PTP) e recuperação de relógio. OX-601 OCXO (oscilador de cristal forno) é outra parte do portfólio da empresa.

As ferramentas de desenvolvimento incluem uma interface gráfica do usuário, quadro de avaliação e notas de aplicação.