"Nostra ZL3073x/63x/64x synchronisation retis instrumentum instrumentorum mensurae, calibratae et modulationis facultates, signanter reducendo in retis instrumentis errori occurrendi gravissimis 5G requisitis" dixit societatis compositionem partium sincere Rami Kanama, qui eam describit ut "flexibilem Architectura ad densitatem canalem necessarii exsequendam, necnon syntheseses humiles jitterarum adiuvant consilium cardium leonum, chartarum linearum, unitates radiophonicae, centrales unitates [cus] et unitates distributae ad retiacula radiophonica 5G [RANs]. .

Societatem petit ITU-T ferire G.8273.2 Classis C 30ns max et emergentes Class D (5ns max) error temporis requisita.

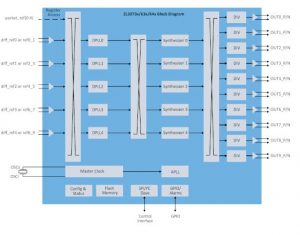

Usque ad quinque independentes DPLL (phase digitalis ansa clausa) canales praesto sunt ad dissipationem 900mW ex sarcina 9 x 9mm. Jitter declaratur 100fs rmat.

Aliae partes suggestuum synchronisation retis sunt licensabiles ZLS30730 algorithmus et Microchip scriptor ZLS30390 IEEE 1588-2008 protocollum machinae ad praecisionem temporis protocolli (PTP) et horologii recuperationis. OX-601 OCXO (cristallus oscillator ovisedus) est alterae partes in librario societatis.

Instrumenta progressio includunt usorem graphicum interfaciem, aestimationem tabulam et notas applicationis.