“Nuestra plataforma de sincronización de red ZL3073x / 63x / 64x implementa capacidades de medición, calibración y ajuste, lo que reduce significativamente el error de tiempo del equipo de red para cumplir con los requisitos 5G más estrictos”, dijo el vicepresidente de componentes de temporización de la compañía, Rami Kanama, quien lo describe como “un sistema flexible La arquitectura para implementar la densidad de canales necesaria, así como los sintetizadores de baja fluctuación, ayudan al diseño de tarjetas de temporización, tarjetas de línea, unidades de radio [RU], unidades centralizadas [CU] y unidades distribuidas [DU] para redes de acceso de radio 5G [RAN]. . "

La compañía afirma cumplir con el estándar ITU-T G.8273.2 Clase C 30ns máx. Y los requisitos emergentes de error de tiempo de Clase D (5ns máx.).

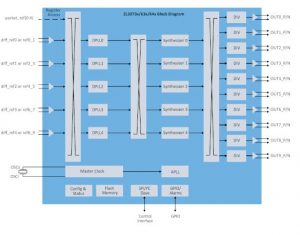

Se encuentran disponibles hasta cinco canales DPLL (bucle de bloqueo de fase digital) independientes para una disipación de 900 mW desde un paquete de 9 x 9 mm. Se afirma que la fluctuación es 100fs rms.

Otras partes de la plataforma de sincronización de red son el algoritmo licenciable ZLS30730 y el motor de protocolo ZLS30390 IEEE 1588-2008 de Microchip para el protocolo de tiempo de precisión (PTP) y la recuperación del reloj. OX-601 OCXO (oscilador de cristal en horno) es otra parte de la cartera de la empresa.

Las herramientas de desarrollo incluyen una interfaz gráfica de usuario, una placa de evaluación y notas de aplicación.