“Platform sinkronisasi jaringan ZL3073x/63x/64x kami menerapkan kemampuan mengukur, mengkalibrasi, dan menyetel, secara signifikan mengurangi kesalahan waktu peralatan jaringan untuk memenuhi persyaratan 5G yang paling ketat,” kata wakil presiden komponen waktu perusahaan Rami Kanama, yang menggambarkannya sebagai “sebuah arsitektur untuk mengimplementasikan kepadatan saluran yang diperlukan, serta synthesizer jitter rendah membantu desain kartu waktu, kartu garis, unit radio [RU], unit terpusat [CU] dan unit terdistribusi [DU] untuk jaringan akses radio 5G [RAN] .”

Perusahaan mengklaim telah mencapai Standar ITU-T G.8273.2 Kelas C 30ns maks dan dan persyaratan kesalahan waktu Kelas D (5ns maks) yang muncul.

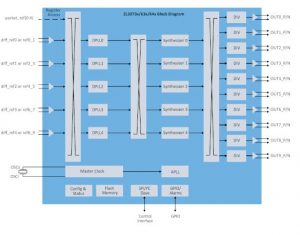

Hingga lima saluran DPLL (digital phase-locked loop) independen tersedia untuk disipasi 900mW dari paket 9 x 9mm. Jitter diklaim 100fs rms.

Bagian lain dari platform sinkronisasi jaringan adalah algoritma ZLS30730 yang dapat dilisensikan dan mesin protokol ZLS30390 IEEE 1588-2008 Microchip untuk protokol waktu presisi (PTP) dan pemulihan jam. OX-601 OCXO (osilator kristal oven) adalah bagian lain dalam portofolio perusahaan.

Alat pengembangan termasuk antarmuka pengguna grafis, papan evaluasi dan catatan aplikasi.