“Our ZL3073x/63x/64x network synchronisation platform implements measure, calibrate and tune capabilities, significantly reducing network equipment time error to meet the most stringent 5G requirements,” said the company’s v-p of timing components Rami Kanama, who describes it as “a flexible architecture for implementing the necessary channel density, as well as low-jitter synthesisers help the design of timing cards, line cards, radio units [RUs], centralised units [CUs] and distributed units [DUs] for 5G radio access networks [RANs].”

The company is claiming to hit ITU-T Standard G.8273.2 Class C 30ns max and and emerging Class D (5ns max) time error requirements.

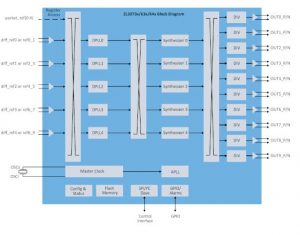

Up to five independent DPLL (digital phase-locked loop) channels are available for a dissipation of 900mW from a 9 x 9mm package. Jitter is claimed to be 100fs rms.

Other parts of the network synchronisation platform are the licensable ZLS30730 algorithm and Microchip’s ZLS30390 IEEE 1588-2008 protocol engine for precision time protocol (PTP) and clock recovery. OX-601 OCXO (ovenised crystal oscillator) is another parts in the company’s portfolio.

Development tools include a graphical user interface, evaluation board and application notes.