Rambus veröffentlicht ein 8.4 Gbit/s HBM3-fähiges Speichersubsystem

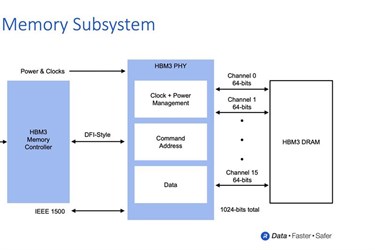

Rambus hat das HBM3-fähige Speicherschnittstellen-Subsystem angekündigt, das aus einem vollständig integrierten PHY und einem digitalen Controller besteht.

Mit der Fähigkeit, Datenraten von bis zu 8.4 Gbit/s zu unterstützen, kann es eine Bandbreite von über einem Terabyte pro Sekunde bereitstellen, mehr als das Doppelte der von High-End-HBM2E-Speichersubsystemen. Rambus verfügt bereits über eine starke Erfolgsbilanz bei der Bereitstellung von HBM2/2E-Speicherschnittstellen und gilt als gut aufgestellt, um Kundenimplementierungen von Beschleunigern mit HBM3-Speicher der nächsten Generation zu unterstützen.

Neben dem vollständig integrierten HBM3-fähigen Speichersubsystem bietet Rambus seinen Kunden Interposer- und Package-Referenzdesigns, um die Markteinführung ihrer Produkte zu beschleunigen.

„Mit der Leistung unseres HBM3-fähigen Speichersubsystems können Designer die Bandbreite bereitstellen, die von den anspruchsvollsten Designs benötigt wird“, sagte Matt Jones, General Manager von Interface IP bei Rambus. „Unsere vollständig integrierte PHY- und digitale Controller-Lösung baut auf unserer breiten installierten Basis von HBM2-Kundenimplementierungen auf und wird durch eine vollständige Palette von Support-Services unterstützt, um die richtige Implementierung für geschäftskritische KI/ML-Designs beim ersten Mal zu gewährleisten.“

Zu den Vorteilen des HBM3-fähigen Speicherschnittstellen-Subsystems gehören:

- Unterstützt eine Datenrate von bis zu 8.4 Gbit/s mit einer Bandbreite von 1.075 Terabyte pro Sekunde (TB/s)

- Reduziert die Komplexität des ASIC-Designs und beschleunigt die Markteinführungszeit mit vollständig integriertem PHY und digitalem Controller

- Bietet volle Bandbreitenleistung in allen Datenverkehrsszenarien

- Unterstützt HBM3-RAS-Funktionen

- Beinhaltet einen integrierten Leistungsaktivitätsmonitor auf Hardwareebene

- Bietet Zugang zu Rambus-System- und SI/PI-Experten, die ASIC-Designern helfen, maximale Signal- und Leistungsintegrität für Geräte und Systeme zu gewährleisten

- Enthält 2.5D-Paket und Interposer-Referenzdesign als Teil der IP-Lizenz

- Verfügt über die LabStation-Entwicklungsumgebung, die eine schnelle Systembereitstellung, Charakterisierung und Fehlersuche ermöglicht

- Ermöglicht höchste Leistung in Anwendungen, einschließlich hochmoderner KI/ML-Schulungen und High-Performance-Computing-(HPC)-Systemen