Rambusが8.4GbpsHBM3対応メモリサブシステムをリリース

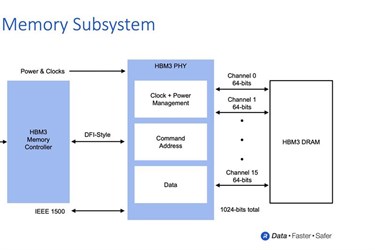

Rambusは、完全に統合されたPHYとデジタルコントローラーで構成されるHBM3対応のメモリインターフェイスサブシステムを発表しました。

最大8.4Gbpsのデータレートをサポートする機能により、テラバイト/秒を超える帯域幅を提供できます。これは、ハイエンドHBM2Eメモリサブシステムの2倍以上です。 ラムバスは、HBM2 / 3Eメモリインターフェイスの展開ですでに強力な実績があり、次世代HBMXNUMXメモリを使用したアクセラレータの顧客の実装をサポートするのに適していると言われています。

完全に統合されたHBM3対応のメモリサブシステムに加えて、Rambusは、製品の市場投入をスピードアップするためのインターポーザーおよびパッケージリファレンスデザインを顧客に提供します。

「HBM3対応のメモリサブシステムによって達成されたパフォーマンスにより、設計者は最も要求の厳しい設計に必要な帯域幅を提供できます」と、RambusのインターフェイスIPのゼネラルマネージャーであるマットジョーンズは述べています。 「当社の完全に統合されたPHYおよびデジタルコントローラーソリューションは、HBM2のお客様の展開の幅広いインストールベースに基づいて構築されており、ミッションクリティカルなAI / ML設計の最初の適切な実装を保証するために、サポートサービスの完全なスイートに支えられています。」

HBM3対応のメモリインターフェイスサブシステムの利点は次のとおりです。

- 最大8.4Gbpsのデータレートをサポートし、1.075テラビット/秒(TB / s)の帯域幅を提供します

- 完全に統合されたPHYとデジタルコントローラーにより、ASIC設計の複雑さを軽減し、市場投入までの時間を短縮します

- すべてのデータトラフィックシナリオで全帯域幅のパフォーマンスを提供します

- HBM3RAS機能をサポート

- 組み込みのハードウェアレベルのパフォーマンスアクティビティモニターが含まれています

- ラムバスシステムとSI / PIの専門家へのアクセスを提供し、ASIC設計者がデバイスとシステムの最大の信号と電力の整合性を確保できるようにします

- IPライセンスの一部として2.5Dパッケージとインターポーザーリファレンスデザインが含まれています

- 迅速なシステムの立ち上げ、特性評価、およびデバッグを可能にするLabStation開発環境を備えています

- 最先端のAI / MLトレーニングやハイパフォーマンスコンピューティング(HPC)システムなどのアプリケーションで最高のパフォーマンスを実現します