Rambus, 8.4Gbps HBM3 지원 메모리 하위 시스템 출시

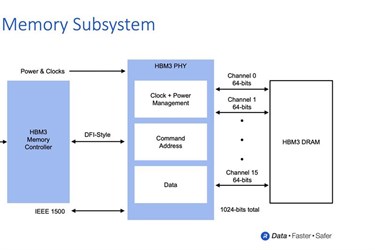

Rambus는 완전히 통합된 PHY와 디지털 컨트롤러로 구성된 HBM3 지원 메모리 인터페이스 하위 시스템을 발표했습니다.

최대 8.4Gbps의 데이터 속도를 지원하는 기능으로 초당 테라바이트 이상의 대역폭을 제공할 수 있으며, 이는 하이엔드 HBM2E 메모리 하위 시스템의 두 배 이상입니다. 이미 HBM2/2E 메모리 인터페이스 배치에 대한 강력한 실적을 보유한 Rambus는 차세대 HBM3 메모리를 사용하는 가속기의 고객 구현을 지원하기에 적합한 위치에 있다고 합니다.

완전히 통합된 HBM3 지원 메모리 하위 시스템 외에도 Rambus는 고객에게 제품 출시 시간을 단축할 수 있는 인터포저 및 패키지 참조 설계를 제공합니다.

Rambus의 인터페이스 IP 제너럴 매니저인 Matt Jones는 “우리의 HBM3 지원 메모리 하위 시스템이 달성한 성능을 통해 설계자는 가장 까다로운 설계에 필요한 대역폭을 제공할 수 있습니다. "우리의 완전히 통합된 PHY 및 디지털 컨트롤러 솔루션은 HBM2 고객 배포의 광범위한 설치 기반을 기반으로 하며 미션 크리티컬 AI/ML 설계를 위한 최초의 올바른 구현을 보장하기 위해 전체 지원 서비스 제품군의 지원을 받습니다."

HBM3 지원 메모리 인터페이스 서브시스템의 이점은 다음과 같습니다.

- 초당 8.4테라바이트(TB/s)의 대역폭을 제공하는 최대 1.075Gbps 데이터 속도 지원

- 완전히 통합된 PHY 및 디지털 컨트롤러로 ASIC 설계 복잡성을 줄이고 시장 출시 시간 단축

- 모든 데이터 트래픽 시나리오에서 전체 대역폭 성능 제공

- HBM3 RAS 기능 지원

- 내장 하드웨어 수준 성능 활동 모니터 포함

- Rambus 시스템 및 SI/PI 전문가에 대한 액세스를 제공하여 ASIC 설계자가 장치 및 시스템에 대한 최대 신호 및 전력 무결성을 보장할 수 있도록 지원

- IP 라이센스의 일부로 2.5D 패키지 및 인터포저 참조 설계 포함

- 빠른 시스템 불러오기, 특성화 및 디버그를 가능하게 하는 LabStation 개발 환경이 특징입니다.

- 최첨단 AI/ML 교육 및 고성능 컴퓨팅(HPC) 시스템을 포함한 애플리케이션에서 최고의 성능 구현