Rambus lanza subsistema de memoria de 8.4 Gbps listo para HBM3

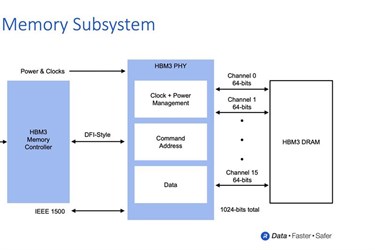

Rambus ha anunciado el subsistema de interfaz de memoria listo para HBM3, que consta de un controlador digital y PHY totalmente integrado.

Con la capacidad de admitir velocidades de datos de hasta 8.4 Gbps, puede entregar más de un terabyte por segundo de ancho de banda, más del doble que los subsistemas de memoria HBM2E de gama alta. Ya con un sólido historial en implementaciones de interfaces de memoria HBM2 / 2E, se dice que Rambus está bien posicionado para respaldar las implementaciones de aceleradores de los clientes que utilizan memoria HBM3 de próxima generación.

Además del subsistema de memoria totalmente integrado listo para HBM3, Rambus ofrece a sus clientes diseños de referencia de intercalador y paquete para acelerar la comercialización de sus productos.

“Con el rendimiento logrado por nuestro subsistema de memoria listo para HBM3, los diseñadores pueden entregar el ancho de banda que necesitan los diseños más exigentes”, dijo Matt Jones, gerente general de Interface IP en Rambus. "Nuestra solución de controlador digital y PHY totalmente integrada se basa en nuestra amplia base instalada de implementaciones de clientes de HBM2 y está respaldada por un conjunto completo de servicios de soporte para garantizar implementaciones correctas por primera vez para diseños de IA / ML de misión crítica".

Los beneficios del subsistema de interfaz de memoria listo para HBM3 incluyen:

- Admite una velocidad de datos de hasta 8.4 Gbps que ofrece un ancho de banda de 1.075 terabytes por segundo (TB / s)

- Reduce la complejidad del diseño ASIC y acelera el tiempo de comercialización con PHY totalmente integrado y controlador digital

- Ofrece un rendimiento de ancho de banda completo en todos los escenarios de tráfico de datos

- Admite funciones HBM3 RAS

- Incluye monitor de actividad de rendimiento a nivel de hardware integrado

- Proporciona acceso al sistema Rambus y a expertos en SI / PI que ayudan a los diseñadores de ASIC a garantizar la máxima integridad de la señal y la alimentación de los dispositivos y sistemas.

- Incluye paquete 2.5D y diseño de referencia de intercalador como parte de la licencia de IP

- Cuenta con un entorno de desarrollo de LabStation que permite una rápida activación, caracterización y depuración del sistema.

- Permite el más alto rendimiento en aplicaciones, incluidos los sistemas de informática de alto rendimiento (HPC) y entrenamiento de IA / ML de última generación