Rambus lance un sous-système de mémoire compatible HBM8.4 à 3 Gbit/s

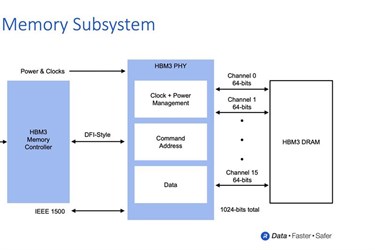

Rambus a annoncé le sous-système d'interface mémoire compatible HBM3, qui se compose d'un PHY et d'un contrôleur numérique entièrement intégrés.

Capable de prendre en charge des débits de données allant jusqu'à 8.4 Gbit/s, il peut fournir plus d'un téraoctet par seconde de bande passante, soit plus du double de celle des sous-systèmes de mémoire haut de gamme HBM2E. Déjà fort d'une solide expérience dans les déploiements d'interfaces mémoire HBM2/2E, Rambus serait bien placé pour prendre en charge les implémentations des clients d'accélérateurs utilisant la mémoire HBM3 de nouvelle génération.

En plus du sous-système de mémoire entièrement intégré compatible HBM3, Rambus fournit à ses clients des conceptions de référence d'interposeur et de boîtier pour accélérer la mise sur le marché de leurs produits.

« Grâce aux performances obtenues par notre sous-système de mémoire compatible HBM3, les concepteurs peuvent fournir la bande passante requise par les conceptions les plus exigeantes », a déclaré Matt Jones, directeur général d'Interface IP chez Rambus. « Notre solution de contrôleur numérique et PHY entièrement intégrée s'appuie sur notre large base installée de déploiements clients HBM2 et s'appuie sur une suite complète de services d'assistance pour garantir une première mise en œuvre correcte pour les conceptions d'IA/ML critiques.

Les avantages du sous-système d'interface mémoire compatible HBM3 incluent :

- Prend en charge un débit de données jusqu'à 8.4 Gbit/s offrant une bande passante de 1.075 téraoctets par seconde (To/s)

- Réduit la complexité de la conception ASIC et accélère le délai de mise sur le marché avec PHY et contrôleur numérique entièrement intégrés

- Fournit des performances de bande passante complète dans tous les scénarios de trafic de données

- Prend en charge les fonctionnalités HBM3 RAS

- Comprend un moniteur d'activité de performance de niveau matériel intégré

- Fournit un accès au système Rambus et aux experts SI/PI aidant les concepteurs d'ASIC à garantir une intégrité maximale du signal et de l'alimentation pour les appareils et les systèmes

- Comprend un package 2.5D et une conception de référence d'interposeur dans le cadre de la licence IP

- Comprend l'environnement de développement LabStation qui permet une mise en place, une caractérisation et un débogage rapides du système

- Permet les performances les plus élevées dans les applications, y compris la formation AI/ML de pointe et les systèmes de calcul haute performance (HPC)