Cum pars seriei RZ/V, novus RZ/V2L accelerator intelligentiae artificialis "DRP-AI" habet, cum frequentia et memoria operativae interfacies ad applicationes in ingressu graduum ascenderunt.

DRP-AI reali temporis coniecturam praebet et processus imaginis cum camera subsidii ut color correctionis et soni reductionem praebet.

In hoc casu describitur "1Top/s/W genus") et minimum YOLOv2 currere potest ad scriptor 28frame.

"Hoc dat clientibus ut applicationes visionis AI-fundatae evolverent, ut punctum terminales et vacuum emundantes robot vacuum, non requirens processus imaginis externae," secundum Renesas.

Venit in 15 mm quadratum vel 21 mm fasciculi quadrati BGA qui acus compatiuntur cum proposito generali existente MPUs, permittens RZ/G2L utentes ad upgrade processus capacis AI.

Cum pars RZ/V2L ambitus evolutionis, Renesas DRP-AI Translator offert, instrumentum quo AI exempla in formatam exsecutivam formam automatice convertit. Forma initus est industria-signum ONNX (apertum network commutatio neural).

RZ/V2L MPUs:

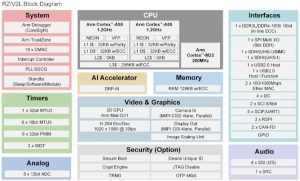

- Dual or single 1.2GHz 64bit Brachium Cortex-A55

- M33 cortex,

- 16bit, unum alveum DDR memoriae interface

- Brachium Mali-G31 3D graphics

- H.264 video cod

- MIPI-CSI et CMOS camerae interfaces parallelae

- MIPI-DSI et interfaces parallelae ostentus

- Memoria cum ECC (errore recognitione et correctione)

- ISP munera ad visionem machinae (usque ad HD) in bibliotheca DRP

- Verified Linux involucrum (VLP) secundum infrastructurae civilis rostris Linux

RZ/V2L Tabulae aestimationis in promptu sunt et praebent: "circuit tabula et tabula extensionis, et includunt copiam virtutis ambitum et ligni sincere".

Potentia procuratio IC optimized pro RZ/V2L in pipelino, exempla coniungendi exspectantur in secundo dimidium huius anni.

RZ/V2L pagina producta hic est