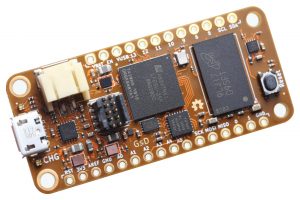

Es basiert auf dem Lattice EPC5-FPGA mit QSPI-Flash-Speicher - abhängig von der Wahl zwischen EPC5-25F (128 Mbit) oder ECP5-85F (512 Mbit) - und bis zu 8 Gbit DDR3 On-Board-Systemspeicher.

Das FPGA ist mit der Open-Source-Toolchain kompatibel und kann mit RISC-V und anderen Softcore-SoCs verwendet werden. Benutzer können über CircuitPython auf das OrangeCrab portieren, auf dem der Interpreter gehostet werden kann, und Entwickler können das FPGA mit Gateware-synthetisiertem HDL als Ziel festlegen.

Die EPC5-FPGAs verfügen über 24k-LUT-Elemente und 10-polige Programmierköpfe. Bei Bedarf gibt es einen Micro-SD-Sockel für zusätzlichen Speicher, der über eine direkte USB-Verbindung mit voller Geschwindigkeit zum FPGA verfügt. Auf den FPGAs kann auch ein RISC-V-Softcore ausgeführt werden.

Mit dem Open-Source-USB-Bootloader können Benutzer über die native USB-Schnittstelle des FPGA eine Verbindung herstellen, um Code hochzuladen und über MicroSD auf die Speicher zuzugreifen. Mit dem Standard-Header 2 × 5, 1.27 mm können Anwendungen auf der USB-Ebene entwickelt werden.

Laut Farnell verfügt der SBC über eine hohe Energieeffizienz für den Netzbetrieb mit einem 100-mA-Batterieladechip, einem LiPo-Batterieanschluss (Typ PH) und einem 48-MHz-Oszillator.