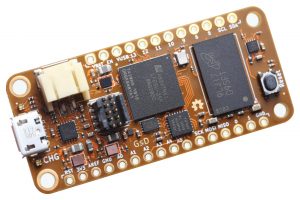

Se basa en el Lattice EPC5-FPGA con memoria flash QSPI, según la elección de EPC5-25F (128 Mbit) o ECP5-85F (512 Mbit), y hasta 8 Gbit DDR3 de memoria del sistema integrada.

La FPGA es compatible con la cadena de herramientas de código abierto y se puede utilizar con RISC-V y otros SoC de núcleo blando. Los usuarios pueden transferir CircuitPython al OrangeCrab, que puede ser el anfitrión del intérprete y los desarrolladores pueden apuntar a la FPGA con HDL sintetizado por gateware.

Los FPGA EPC5 tienen elementos LUT de 24k y encabezados de programación de 10 pines. Hay una toma Micro SD para almacenamiento adicional, si es necesario, que tiene conexión USB directa de velocidad completa a la FPGA. Los FPGA también pueden ejecutar un núcleo de software RISC-V.

El cargador de arranque USB de código abierto permite a los usuarios conectarse a través de la interfaz USB nativa de la FPGA para cargar el código y acceder a las memorias a través de MicroSD. El cabezal estándar de 2 × 5, 1.27 mm se puede utilizar para desarrollar aplicaciones en la capa USB.

El SBC tiene una alta eficiencia energética para el funcionamiento de la red eléctrica, dice Farnell, con un chip cargador de batería de 100 mA, un conector de batería LiPo (tipo PH) y un oscilador de 48 MHz.