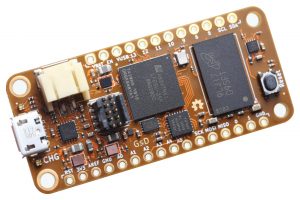

É baseado no Lattice EPC5-FPGA com memória flash QSPI - dependendo da escolha de EPC5-25F (128-Mbit) ou ECP5-85F (512-Mbit) - e até 8 Gbit DDR3 de memória de sistema on-board.

O FPGA é compatível com o conjunto de ferramentas de código aberto e pode ser usado com RISC-V e outros SoCs de núcleo suave. Os usuários podem portar através do CircuitPython para o OrangeCrab, que pode hospedar o intérprete e os desenvolvedores podem direcionar o FPGA com HDL sintetizado por gateware.

Os FPGAs EPC5 têm elementos LUT de 24k e cabeçalhos de programação de 10 pinos. Há um soquete Micro SD para armazenamento adicional, se necessário, com conexão USB direta de velocidade total ao FPGA. Os FPGAs também podem executar um soft core RISC-V.

O bootloader USB de código aberto permite que os usuários se conectem por meio da interface USB nativa do FPGA para fazer upload de código e acessar as memórias por MicroSD. O conector padrão de 2 × 5, 1.27 mm pode ser usado para desenvolver aplicativos na camada USB.

O SBC tem alta eficiência energética para operação com rede elétrica, diz Farnell, com um chip carregador de bateria de 100mA, um conector de bateria LiPo (tipo PH) e um oscilador de 48 MHz.