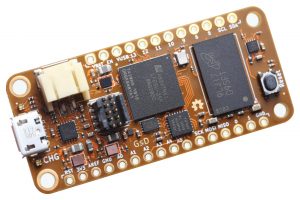

Он основан на Lattice EPC5-FPGA / ПРОГРАММИРУЕМАЯ ПОЛЬЗОВАТЕЛЕМ ВЕНТИЛЬНАЯ МАТРИЦА с флэш-памятью QSPI - в зависимости от выбора EPC5-25F (128 Мбит) или ECP5-85F (512 Мбит) - и до 8 Гбит встроенной системной памяти DDR3.

FPGA совместима с набором инструментов с открытым исходным кодом и может использоваться с RISC-V и другими SoC с программным ядром. Пользователи могут переносить через CircuitPython на OrangeCrab, который может быть хостом для интерпретатора, а разработчики могут нацеливаться на FPGA с помощью синтезированного шлюзом HDL.

ПЛИС EPC5 имеют 24k LUT-элементов и 10-контактные программные заголовки. При необходимости имеется разъем Micro SD для дополнительного хранилища, обеспечивающий прямое подключение USB к ПЛИС на полной скорости. ПЛИС также могут работать с программным ядром RISC-V.

Загрузчик USB с открытым исходным кодом позволяет пользователям подключаться через собственный интерфейс USB ПЛИС для загрузки кода и доступа к памяти через MicroSD. Стандартный заголовок 2 × 5, 1.27 мм может использоваться для разработки приложений на уровне USB.

По словам Фарнелла, SBC обладает высокой энергоэффективностью для работы от сети, с микросхемой зарядного устройства 100 мА, разъемом для литий-полимерной батареи (тип PH) и генератором 48 МГц.