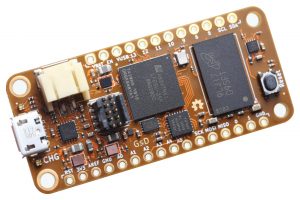

Ini didasarkan pada Lattice EPC5-FPGA dengan memori flash QSPI - tergantung pada pilihan EPC5-25F (128-Mbit) atau ECP5-85F (512-Mbit) - dan hingga 8-Gbit DDR3 memori sistem on-board.

FPGA kompatibel dengan toolchain sumber terbuka dan dapat digunakan dengan RISC-V dan SoC inti lunak lainnya. Pengguna dapat melakukan port melalui CircuitPython ke OrangeCrab yang dapat menjadi host penerjemah dan pengembang dapat menargetkan FPGA dengan gateware yang disintesis HDL.

FPGA EPC5 memiliki elemen 24k LUT dan header pemrograman 10-pin. Ada soket Micro SD untuk penyimpanan tambahan, jika diperlukan, yang memiliki koneksi USB langsung berkecepatan penuh ke FPGA. FPGA juga dapat menjalankan inti lunak RISC-V.

Bootloader USB sumber terbuka memungkinkan pengguna untuk terhubung melalui antarmuka USB asli FPGA untuk mengunggah kode dan mengakses memori melalui MicroSD. Header standar 2 × 5, 1.27mm dapat digunakan untuk mengembangkan aplikasi pada lapisan USB.

SBC memiliki efisiensi daya yang tinggi untuk operasi catu daya, kata Farnell, dengan chip pengisi daya baterai 100mA, konektor baterai LiPo (tipe PH) dan osilator 48-MHz.