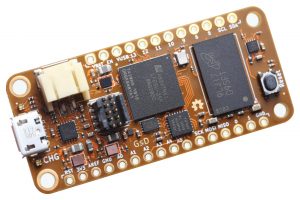

Il est basé sur le Lattice EPC5-FPGA avec mémoire flash QSPI - selon le choix de l'EPC5-25F (128 Mbit) ou ECP5-85F (512 Mbit) - et jusqu'à 8 Gbit DDR3 de mémoire système intégrée.

Le FPGA est compatible avec la chaîne d'outils open source et peut être utilisé avec RISC-V et d'autres SoC soft core. Les utilisateurs peuvent porter via CircuitPython vers OrangeCrab qui peut héberger l'interpréteur et les développeurs peuvent cibler le FPGA avec du HDL synthétisé par gateware.

Les FPGA EPC5 ont des éléments LUT 24k et des en-têtes de programmation à 10 broches. Il y a une prise Micro SD pour un stockage supplémentaire, si nécessaire, qui dispose d'une connexion USB directe à pleine vitesse au FPGA. Les FPGA peuvent également exécuter un noyau souple RISC-V.

Le chargeur de démarrage USB open-source permet aux utilisateurs de se connecter via l'interface USB native du FPGA pour télécharger du code et accéder aux mémoires via MicroSD. L'en-tête standard 2 × 5, 1.27 mm peut être utilisé pour développer des applications sur la couche USB.

Le SBC a une efficacité énergétique élevée pour le fonctionnement sur secteur, dit Farnell, avec une puce de chargeur de batterie de 100 mA, un connecteur de batterie LiPo (type PH) et un oscillateur à 48 MHz.