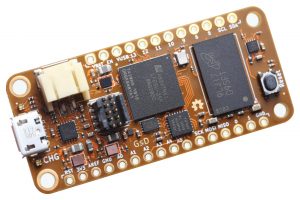

Ia berdasarkan pada Lattice EPC5-FPGA dengan memori flash QSPI - bergantung pada pilihan EPC5-25F (128-Mbit) atau ECP5-85F (512-Mbit) - dan memori sistem on-board sehingga 8-Gbit DDR3.

FPGA serasi dengan rantai alat sumber terbuka dan boleh digunakan dengan RISC-V dan SoC inti lembut yang lain. Pengguna boleh mengarahkan CircuitPython ke OrangeCrab yang boleh menjadi host jurubahasa dan pembangun boleh menargetkan FPGA dengan HDL yang disintesis gateware.

EPC5 FPGA mempunyai elemen LUT 24k dan tajuk pengaturcaraan 10-pin. Terdapat soket Micro SD untuk penyimpanan tambahan, jika diperlukan, yang mempunyai sambungan USB langsung berkelajuan penuh ke FPGA. FPGA juga boleh menjalankan inti lembut RISC-V.

Pemuat but USB sumber terbuka membolehkan pengguna menyambung melalui antara muka USB asli FPGA untuk memuat naik kod dan mengakses kenangan melalui MicroSD. Header standard 2 × 5, 1.27mm dapat digunakan untuk mengembangkan aplikasi pada lapisan USB.

SBC mempunyai kecekapan kuasa tinggi untuk operasi bekalan utama, kata Farnell, dengan cip pengecas bateri 100mA, penyambung bateri LiPo (jenis PH) dan pengayun 48-MHz.