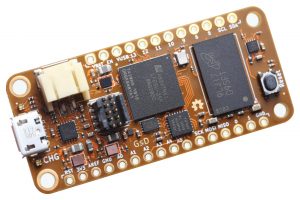

Fundatur in cancellos EPC5-FPGA cum memoria mico QSPI — secundum electionem EPC5-25F (128-Mbit) vel ECP5-85F (512-Mbit) — et usque ad 8-Gbit DDR3 in tabula systematis memoriae.

FPGA cum instrumento aperto fonte compatitur et cum RISC-V et aliis nucleis SoCs mollibus adhiberi potest. Users in CircuitPython ad OrangeCrab traicere possunt qui interpretem et tincturae exercitum esse possunt, FPGA portarum synthesis HDL oppugnare possunt.

EPC5 FPGAs habent 24k LUT elementa et 10-pinum capitis capitis programmatio. Est nervus Micro SD pro additamento repositorii, si opus fuerit, quae plenam celeritatem USB ad FPGA connexionem habet. Potest etiam FPGAs currere nucleum mollem RISC-V.

Fons apertus USB bootloader dat utentes coniungere per interfaciem FPGA indigena USB ad notas notas et ad memoriam accessere per MicroSD. Vexillum 2×5, 1.27mm caput adhiberi potest ad applicationes explicandas in tabulato USB.

SBC altam vim habet efficientiam ad operandi principales copiam, dicit Farnell, cum 100mA in patina altilium, a iungo altilium LiPo (PH type) et 48-MHz oscillatoris.