Der geplante Roboter benötigt konventionelle Verarbeitung für die Planung und Steuerung sowie eine KI-Verarbeitung mit ~100 Top/s Spitze für die visionsbasierte Umgebungserkennung, mit geringer Verlustleistung, um die Notwendigkeit eines Lüfters zu vermeiden – der Verbrauch des 14-nm-IC beträgt ~5 W.

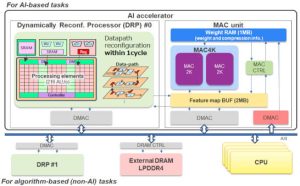

Es wurde eine heterogene Mikroprozessorarchitektur gewählt, die einen dynamisch rekonfigurierbaren KI-Beschleuniger umfasst, der 130Top/s bei 23.9Top/s/W (von 0.8V) mit INT8-Daten (8-Bit-Ganzzahl) liefern kann.

„Die Messung erfolgte mithilfe eines idealen CNN-Modells – nicht eines tatsächlichen Modells – bestehend aus einer einzelnen Faltungsschicht mit maximaler Sparsity“, sagte das Unternehmen gegenüber Electronics Weekly. „Mit tatsächlichen KI-Modellen – ResNet50, YOLOV2 und deeplabV3 – haben wir 9-11Top/s/W erreicht.“

Der Unterschied besteht darin, dass dieser Prozessor Berechnungen mit Nullen in der Gewichtsmatrix dynamisch bereinigt – seine Architektur ermöglicht es ihm, eine effizientere „unstrukturierte“ Bereinigung durchzuführen und gleichzeitig parallele Berechnungen beizubehalten. Renesas nennt es „N:M-Pruning“ und führt zu 80–90 % weniger Berechnungen, wenn viele Gewichte Null sind – eine „sparse Matrix“ –, während die Leistung bei vollständig dichten Matrizen, bei denen alle Gewichte nicht Null sind, auf ~8Top/s sinkt. null.

Sein Prozessor verfügt über 216 Verarbeitungselemente, die innerhalb eines Taktzyklus neu konfiguriert werden können, sodass die Hardware für jeden Schritt eines mehrstufigen Algorithmus optimiert werden kann.

„Beispielsweise erfordert SLAM [gleichzeitige Lokalisierung und Kartierung] mehrere Programmierprozesse für die Roboterpositionserkennung parallel zur Umgebungserkennung durch visuelle KI-Verarbeitung“, so das Unternehmen. „Renesas demonstrierte den Betrieb dieses SLAM durch sofortige Programmumschaltung mit dem dynamisch rekonfigurierbaren Prozessor und den parallelen Betrieb des KI-Beschleunigers und der CPU, was zu etwa 17-mal schnelleren Betriebsgeschwindigkeiten und einer etwa 12-mal höheren Betriebsleistungseffizienz als die eingebettete CPU allein führte.“

Nach Angaben des Unternehmens ist dies Technologie ist für seine Mikroprozessorserie RZ/V für Bildverarbeitungsanwendungen bestimmt.

ISSCC 2024-Papier 20.3: Ein KI-Beschleuniger mit 23.9 TOPS/W bei 0.8 V und 130 TOPS mit 16-fach leistungsbeschleunigtem Pruning in einer heterogenen eingebetteten 14-nm-MPU für Echtzeit-Roboteranwendungen

ISSCC, die jährliche International Solid-State Circuits Conference in San Francisco, ist das weltweite Schaufenster für Fortschritte bei Schaltkreisen für ICs – die Teilnehmer werden im wahrsten Sinne des Wortes mit dem neuesten Stand der Technik vertraut gemacht.

Bildnachweis: ISSCC 2024 Renesas