Il robot previsto necessita di un’elaborazione convenzionale per la pianificazione e il controllo, insieme all’elaborazione dell’intelligenza artificiale a un picco di ~ 100 Top/s per il riconoscimento ambientale basato sulla visione, con una bassa dissipazione di potenza per evitare la necessità di una ventola – il consumo dell’IC da 14 nm è di ~ 5 W.

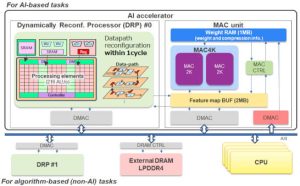

È stata scelta un'architettura eterogenea del microprocessore, che include un acceleratore AI riconfigurabile dinamicamente in grado di fornire 130 Top/s a 23.9 Top/s/W (da 0.8 V) con dati INT8 (intero a 8 bit).

“È stato misurato utilizzando un modello CNN ideale – non un modello reale – costituito da un singolo strato di convoluzione con la massima scarsità”, ha detto l’azienda a Electronics Weekly. “Con i modelli AI reali – ResNet50, YOLOV2 e deeplabV3 – abbiamo ottenuto 9-11Top/s/W.”

La differenza è dovuta al fatto che questo processore elimina dinamicamente i calcoli con zeri nella matrice dei pesi: la sua architettura gli consente di eseguire un'eliminazione "non strutturata" più efficiente mantenendo il calcolo parallelo. Renesas lo chiama "potatura N:M" e si traduce in calcoli dell'80 – 90% in meno in cui molti pesi sono pari a zero - una "matrice sparsa" - mentre le prestazioni scendono a ~8Top/s per matrici completamente dense in cui tutti i pesi non sono- zero.

Il suo processore ha 216 elementi di elaborazione, che possono essere riconfigurati entro un ciclo di clock, consentendo di ottimizzare l'hardware per ogni passaggio di un algoritmo multi-step.

"Ad esempio, SLAM [localizzazione e mappatura simultanea] richiede più processi di programmazione per il riconoscimento della posizione del robot in parallelo con il riconoscimento dell'ambiente mediante l'elaborazione dell'intelligenza artificiale visiva", secondo l'azienda. "Renesas ha dimostrato il funzionamento di questo SLAM attraverso la commutazione istantanea del programma con il processore riconfigurabile dinamicamente e il funzionamento parallelo dell'acceleratore AI e della CPU, ottenendo velocità operative circa 17 volte più elevate e un'efficienza energetica operativa circa 12 volte superiore rispetto alla sola CPU integrata."

Secondo l'azienda, questo la tecnologia è destinata alla serie RZ/V di microprocessori per applicazioni di visione.

Documento 2024 dell'ISSCC 20.3: Un acceleratore AI da 23.9 TOPS/W a 0.8 V, 130 TOPS con potatura 16 volte accelerabile in termini di prestazioni in MPU incorporata eterogenea da 14 nm per applicazioni robotiche in tempo reale

L'ISSCC, la conferenza annuale internazionale sui circuiti a stato solido che si tiene a San Francisco, è la vetrina mondiale per i progressi dei circuiti mirati ai circuiti integrati: i partecipanti sono esposti, letteralmente, allo stato dell'arte.

Credito immagine: ISSCC 2024 Renesas