De geplande robot heeft conventionele verwerking nodig voor planning en controle, naast AI-verwerking met een piek van ~100Top/s voor op visie gebaseerde omgevingsherkenning, met een lage vermogensdissipatie om de noodzaak van een ventilator te vermijden – het verbruik van de 14nm IC is ~5W.

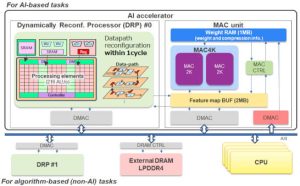

Er werd gekozen voor een heterogene microprocessorarchitectuur, die een dynamisch herconfigureerbare AI-versneller omvat die 130Top/s kan leveren bij 23.9Top/s/W (vanaf 0.8V) met INT8 (8bit integer) data.

“Het werd gemeten met behulp van een ideaal CNN-model – niet een feitelijk model – bestaande uit een enkele convolutielaag met maximale dunheid”, vertelde het bedrijf aan Electronics Weekly. “Met daadwerkelijke AI-modellen – ResNet50, YOLOV2 en deeplabV3 – behaalden we 9-11Top/s/W.”

Het verschil is dat deze processor berekeningen met nullen in de gewichtsmatrix dynamisch wegsnoeit. Dankzij de architectuur kan hij efficiënter 'ongestructureerd' snoeien, terwijl parallelle berekeningen behouden blijven. Renesas noemt het 'N:M snoeien', en het resulteert in 80 – 90% minder berekeningen waarbij veel gewichten nul zijn – een 'sparse matrix' – terwijl de prestaties dalen naar ~8Top/s voor volledig dichte matrices waarbij alle gewichten niet- nul.

De processor heeft 216 verwerkingselementen, die binnen één klokcyclus opnieuw kunnen worden geconfigureerd, waardoor de hardware voor elke stap van een meerstapsalgoritme kan worden geoptimaliseerd.

“SLAM [gelijktijdig lokaliseren en in kaart brengen] vereist bijvoorbeeld meerdere programmeerprocessen voor robotpositieherkenning, parallel met omgevingsherkenning door vision AI-verwerking”, aldus het bedrijf. “Renesas demonstreerde de werking van deze SLAM door middel van onmiddellijke programmawisseling met de dynamisch herconfigureerbare processor en parallelle werking van de AI-accelerator en CPU, resulterend in ongeveer 17 keer snellere werkingssnelheden en ongeveer 12 keer hogere operationele energie-efficiëntie dan de ingebouwde CPU alleen.”

Volgens het bedrijf is dit technologie is bestemd voor zijn RZ/V-serie microprocessors voor vision-toepassingen.

ISSCC 2024 paper 20.3: Een 23.9TOPS/W @ 0.8V, 130TOPS AI-versneller met 16× prestatieversnellbare snoei in 14nm heterogene ingebedde MPU voor real-time robottoepassingen

ISSCC, de jaarlijkse International Solid-State Circuits Conference in San Francisco, is 's werelds etalage voor vooruitgang op het gebied van circuits gericht op IC's. Deelnemers worden letterlijk blootgesteld aan de nieuwste stand van de techniek.

Afbeelding tegoed: ISSCC 2024 Renesas