Le robot prévu a besoin d'un traitement conventionnel pour la planification et le contrôle, ainsi que d'un traitement IA à un pic d'environ 100 Top/s pour la reconnaissance environnementale basée sur la vision, avec une faible dissipation de puissance pour éviter le besoin d'un ventilateur - la consommation du circuit intégré de 14 nm est d'environ 5 W.

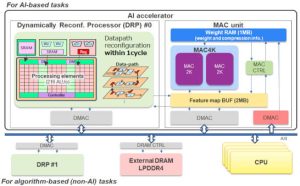

Une architecture de microprocesseur hétérogène a été choisie, qui comprend un accélérateur d'IA reconfigurable dynamiquement qui peut fournir 130 Top/s à 23.9 Top/s/W (à partir de 0.8 V) avec des données INT8 (entier 8 bits).

"Il a été mesuré en utilisant un modèle CNN idéal – et non un modèle réel – composé d'une seule couche de convolution avec une parcimonie maximale", a déclaré la société à Electronics Weekly. "Avec les modèles d'IA réels – ResNet50, YOLOV2 et deeplabV3 – nous avons obtenu 9-11Top/s/W."

La différence réside dans le fait que ce processeur supprime dynamiquement les calculs contenant des zéros dans la matrice de poids – son architecture lui permet d'effectuer un élagage « non structuré » plus efficace tout en conservant les calculs parallèles. Renesas appelle cela « élagage N:M », et il en résulte 80 à 90 % de calculs en moins lorsque de nombreux poids sont nuls – une « matrice clairsemée » – tandis que les performances chutent à ~8Top/s pour des matrices entièrement denses où tous les poids sont non-évalués. zéro.

Son processeur dispose de 216 éléments de traitement, qui peuvent être reconfigurés en un cycle d'horloge, permettant d'optimiser le matériel pour chaque étape d'un algorithme à plusieurs étapes.

« Par exemple, le SLAM [localisation et cartographie simultanées] nécessite plusieurs processus de programmation pour la reconnaissance de la position du robot en parallèle avec la reconnaissance de l'environnement par le traitement de l'IA de vision », selon l'entreprise. « Renesas a démontré le fonctionnement de ce SLAM grâce à une commutation de programme instantanée avec le processeur reconfigurable dynamiquement et au fonctionnement parallèle de l'accélérateur d'IA et du processeur, ce qui entraîne des vitesses de fonctionnement environ 17 fois plus rapides et une efficacité énergétique de fonctionnement environ 12 fois supérieure à celle du processeur intégré seul. »

Selon l'entreprise, ce sans souci est destiné à sa série de microprocesseurs RZ/V pour les applications de vision.

Article ISSCC 2024 20.3 : Un accélérateur d'IA de 23.9TOPS/W à 0.8V, 130TOPS avec un élagage 16× des performances accélérées dans un MPU intégré hétérogène de 14 nm pour les applications robotiques en temps réel

L'ISSCC, la conférence internationale annuelle sur les circuits à semi-conducteurs qui se tient à San Francisco, est la vitrine mondiale des avancées en matière de circuits destinés aux circuits intégrés. Les participants sont littéralement exposés à l'état de l'art.

Crédit image : ISSCC 2024 Renesas