Предполагаемому роботу требуется традиционная обработка для планирования и управления, а также обработка искусственного интеллекта с пиковой скоростью ~ 100 Топ/с для распознавания окружающей среды на основе зрения, с низким рассеиванием мощности, чтобы избежать необходимости в вентиляторе — потребление 14-нм микросхемы составляет ~ 5 Вт.

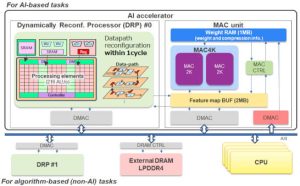

Была выбрана гетерогенная архитектура микропроцессора, которая включает в себя динамически реконфигурируемый ускоритель искусственного интеллекта, который может обеспечивать скорость 130 Топ/с при 23.9 Топ/с/Вт (от 0.8 В) с данными INT8 (8-битное целое число).

«Оно было измерено с использованием идеальной модели CNN, а не реальной модели, состоящей из одного слоя свертки с максимальной разреженностью», — сообщила компания Electronics Weekly. «С реальными моделями ИИ — ResNet50, YOLOV2 и deeplabV3 — мы получили 9-11Top/s/W».

Разница в том, что этот процессор динамически отсекает вычисления с нулями в весовой матрице — его архитектура позволяет ему выполнять более эффективное «неструктурированное» сокращение, сохраняя при этом параллельные вычисления. Renesas называет это «обрезкой N:M», и это приводит к уменьшению количества вычислений на 80–90%, когда многие веса равны нулю (разреженная матрица), в то время как производительность падает до ~ 8Top/s для полностью плотных матриц, где все веса не являются нуль.

Его процессор имеет 216 обрабатывающих элементов, которые можно переконфигурировать за один такт, что позволяет оптимизировать аппаратное обеспечение для каждого шага многошагового алгоритма.

«Например, SLAM [одновременная локализация и картографирование] требует нескольких процессов программирования для распознавания положения робота параллельно с распознаванием окружающей среды с помощью обработки машинного зрения», — сообщают в компании. «Renesas продемонстрировала работу этого SLAM посредством мгновенного переключения программ с помощью динамически реконфигурируемого процессора и параллельной работы ускорителя искусственного интеллекта и центрального процессора, что привело к примерно в 17 раз более высокой скорости работы и примерно в 12 раз более высокой эффективности энергопотребления, чем только у встроенного процессора».

По данным компании, это technology предназначена для микропроцессоров серии RZ/V для систем машинного зрения.

Документ 2024 ISSCC 20.3: ИИ-ускоритель мощностью 23.9 TOPS/Вт при напряжении 0.8 В, 130 TOPS с 16-кратным ускорением производительности в 14-нм гетерогенном встроенном MPU для роботизированных приложений реального времени.

ISSCC, ежегодная Международная конференция по полупроводниковым схемам в Сан-Франциско, является мировой витриной схемотехнических достижений, направленных на микросхемы. Участники в буквальном смысле знакомятся с новейшими достижениями.

Изображение предоставлено: ISSCC 2024 Renesas