O robô previsto precisa de processamento convencional para planejamento e controle, juntamente com processamento de IA com pico de ~100Top/s para reconhecimento ambiental baseado em visão, com baixa dissipação de energia para evitar a necessidade de um ventilador – o consumo do IC de 14nm é de ~5W.

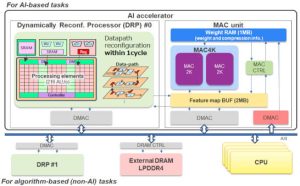

Foi escolhida uma arquitetura de microprocessador heterogêneo, que inclui um acelerador de IA dinamicamente reconfigurável que pode fornecer 130Top/s a 23.9Top/s/W (de 0.8V) com dados INT8 (número inteiro de 8 bits).

“Foi medido usando um modelo CNN ideal – não um modelo real – que consiste em uma única camada de convolução com dispersão máxima”, disse a empresa à Electronics Weekly. “Com modelos reais de IA – ResNet50, YOLOV2 e deeplabV3 – obtivemos 9-11Top/s/W.”

A diferença é que este processador elimina dinamicamente os cálculos com zeros na matriz de pesos – sua arquitetura permite que ele execute uma poda 'não estruturada' mais eficiente enquanto mantém a computação paralela. Renesas chama isso de 'poda N:M' e resulta em 80 a 90% menos cálculos onde muitos pesos são zero - uma 'matriz esparsa' - enquanto o desempenho cai para ~8Top/s para matrizes totalmente densas onde todos os pesos são não- zero.

Seu processador possui 216 elementos de processamento, que podem ser reconfigurados dentro de um ciclo de clock, permitindo que o hardware seja otimizado para cada etapa de um algoritmo multietapas.

“Por exemplo, SLAM [localização e mapeamento simultâneos] requer vários processos de programação para reconhecimento da posição do robô em paralelo com o reconhecimento do ambiente por processamento de IA de visão”, segundo a empresa. “A Renesas demonstrou operar este SLAM por meio de comutação instantânea de programa com o processador dinamicamente reconfigurável e operação paralela do acelerador de IA e CPU, resultando em velocidades de operação cerca de 17 vezes mais rápidas e eficiência de energia operacional cerca de 12 vezes maior do que apenas a CPU incorporada.”

Segundo a empresa, este tecnologia é destinada à sua série RZ/V de microprocessadores para aplicações de visão.

Artigo ISSCC 2024 20.3: Um acelerador AI 23.9TOPS/W @ 0.8V, 130TOPS com poda de desempenho acelerável de 16× em MPU heterogêneo incorporado de 14nm para aplicações de robôs em tempo real

ISSCC, a Conferência Internacional Anual de Circuitos de Estado Sólido em São Francisco, é a vitrine mundial para avanços em circuitos voltados para CIs – os participantes são expostos, literalmente, ao que há de mais moderno.

Crédito da imagem: ISSCC 2024 Renesas