El robot previsto necesita procesamiento convencional para la planificación y el control, junto con procesamiento de IA a un pico de ~100 Top/s para el reconocimiento ambiental basado en la visión, con baja disipación de energía para evitar la necesidad de un ventilador: el consumo del IC de 14 nm es de ~5 W.

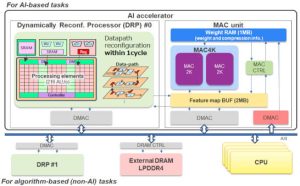

Se eligió una arquitectura de microprocesador heterogénea, que incluye un acelerador de IA reconfigurable dinámicamente que puede ofrecer 130 Top/s a 23.9 Top/s/W (desde 0.8 V) con datos INT8 (entero de 8 bits).

"Se midió utilizando un modelo CNN ideal, no un modelo real, que consta de una única capa convolucional con la máxima escasez", dijo la compañía a Electronics Weekly. "Con modelos de IA reales (ResNet50, YOLOV2 y deeplabV3) obtuvimos 9-11Top/s/W".

La diferencia se debe a que este procesador elimina dinámicamente los cálculos con ceros en la matriz de peso; su arquitectura le permite realizar una poda "no estructurada" más eficiente mientras conserva el cálculo paralelo. Renesas lo llama 'poda N:M' y da como resultado entre un 80 y un 90 % menos de cálculos donde muchos pesos son cero (una 'matriz dispersa'), mientras que el rendimiento cae a ~8Top/s para matrices completamente densas donde todos los pesos no son cero.

Su procesador tiene 216 elementos de procesamiento, que se pueden reconfigurar dentro de un ciclo de reloj, lo que permite optimizar el hardware para cada paso de un algoritmo de varios pasos.

"Por ejemplo, SLAM [simultáneamente localización y mapeo] requiere múltiples procesos de programación para el reconocimiento de la posición del robot en paralelo con el reconocimiento del entorno mediante el procesamiento de IA visual", según la empresa. "Renesas demostró el funcionamiento de este SLAM mediante la conmutación instantánea de programas con el procesador dinámicamente reconfigurable y el funcionamiento paralelo del acelerador de IA y la CPU, lo que da como resultado velocidades de funcionamiento aproximadamente 17 veces más rápidas y aproximadamente 12 veces mayor eficiencia energética operativa que la CPU integrada sola".

Según la empresa, este la tecnología está destinado a su serie RZ/V de microprocesadores para aplicaciones de visión.

Documento 2024 de ISSCC 20.3: Un acelerador de IA de 23.9 TOPS/W a 0.8 V y 130 TOPS con poda de rendimiento acelerable 16× en MPU integrada heterogénea de 14 nm para aplicaciones de robots en tiempo real

ISSCC, la Conferencia Internacional anual sobre Circuitos de Estado Sólido que se celebra en San Francisco, es el escaparate mundial de los avances en circuitos destinados a los circuitos integrados: los asistentes están expuestos, literalmente, a lo último en tecnología.

Crédito de la imagen: ISSCC 2024 Renesas