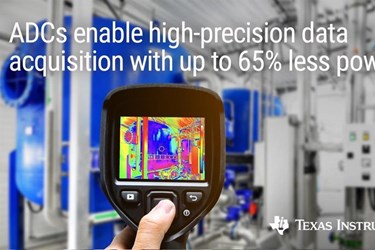

טקסס אינסטרומנטס משיקה משפחת SAR ADC חדשה

טקסס אינסטרומנטס (TI) הרחיבה את תיק ממירי הנתונים המהירים שלה עם משפחה חדשה של ממירי אנלוגי לדיגיטלי (SAR) אנלוגי לדיגיטלי (SAR), שיאפשרו רכישת נתונים ברמת דיוק גבוהה בתכנונים תעשייתיים.

משפחת ADC3660 כוללת טווח דינמי מהשורה הראשונה עם צריכת חשמל נמוכה, וכוללת שמונה ADCs SAR ברזולוציה של 14, 16 ו -18 ביט במהירויות דגימה שנע בין 10 ל 125 MSPS, מה שמסייע למעצבים לשפר את רזולוציית האות, להאריך את חיי הסוללה. ולחזק את הגנת המערכת.

בלולאת בקרה דיגיטלית מהירה, ה- ADC פועל במערכת מורכבת להגיב לשינויים מהירים ב מתח או הנוכחי כדי לסייע במניעת פגיעה יקרה ברכיבים קריטיים במערכות ניהול צריכת חשמל וזה הופך להיות חשוב יותר עבור המערכת לקבל החלטות מהירות למניעת כשל במערכת, מה שמצריך דיוק גבוה יותר במהירויות מהירות יותר.

באמצעות משפחת ADC3660, מעצבי מערכות יכולים להשיג זמן אחזור של ADC בשעון אחד (8 ns) עם ADC125 14-MSPS, 3664 סיביות, כפול ערוץ. השהיה הנמוכה במיוחד של המשפחה מאפשרת לולאות בקרה דיגיטליות מהירות במגוון רחב של מערכות תעשייתיות לניטור מדויק יותר ולהגיב לנקודות מתח וזרם, מה שמגדיל את דיוק הכלים ביישומים כמו סמיקונדקטור מערכות ייצור.

עד כה, מהנדסים שתכננו מערכות תעשייתיות נאלצו לבחור בין ביצועי רעש מעולים לבין צריכת חשמל נמוכה. משפחת ADC3660 מבטלת את המסחר הזה.

לדוגמא, ה- ADC3683 משפר את ביצועי הרעש ביישומי תדרים צרים כמו מכשירי רדיו הגנה ניידים, ומציע יחס אות לרעש (SNR) של 84.2 dB וצפיפות ספקטרלית רעש של -160 dBFS / הרץ תוך שמירה על צריכת חשמל נמוכה של 94 mW לערוץ.

מהירויות הדגימה הגבוהות של משפחת ADC3660 ותכונות משולבות עוזרים למעצבים להפחית את מספר הרכיבים במערכות שלהם. ה- ADC3683, לדוגמא, המדגם ארבע פעמים מהר יותר מהתקני 18 סיביות מתחרים בצפיפות הערוץ כפולה מאפשר דגימת יתר, טכניקה שמרחיקה הרמוניות מהאות הרצוי. זה מאפשר למעצבים להפחית את מורכבות המסננים נגד שיוך ושיפור רכיבי המערכת בכ- 75%.

תכונות אחרות המפחיתות את מורכבות העיצוב כוללות אפשרויות דצימציה על-שבב המאפשרות למעצבים להסיר בקלות רעשים והרמוניות לא רצויות במערכת ולהגביר את ה-SNR והטווח הדינמי הנטול מזויפים עד ל-15dB. אפשרויות חיסול אלה, יחד עם תחמוצת המתכת המשלימה סמיקונדקטור ממשק (CMOS), מאפשר למתכננים להשתמש ב-ADCs אלה עם מעבדים מבוססי Arm או מעבדי אותות דיגיטליים במקום מערכי שערים הניתנים לתכנות בשטח (FPGAs), אשר יכולים לסייע בהורדת עלות המערכת.

בנוסף, ממיר למטה דיגיטלי משולב עם מתנד נשלט מספרית מורכב מפחית את כמות משאבי המעבד הנדרשים.