يتعاون SiFive مع Imperas ، ويؤهل النماذج

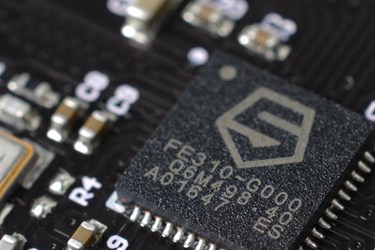

أعلنت شركة Imperas Software ، المتخصصة في الأنظمة الأساسية الافتراضية ومحاكاة البرامج عالية الأداء ، أن SiFive ، الشركة الرائدة في الصناعة في معالجات RISC-V وحلول السيليكون ، قد قامت بتأهيل نماذجها للمجموعة الكاملة من معالج SiFive Core IP Portfolio.

تعد نماذج المحاكاة نقطة انطلاق أساسية للاستكشاف المعماري لشركة SoC المبكرة ، حيث يستخدم مصممو النظام منصات افتراضية لاختبار أحمال عمل التطبيقات الكاملة ومجموعات البيانات لتحسين التكوينات متعددة النواة.

مع تقدم تصميم وتطوير الأجهزة بناءً على هذا المخطط الوظيفي ، فإن نموذج المحاكاة هو الأساس الذي يدعم النماذج الأولية الافتراضية لتطوير البرامج المبكرة قبل توفر أجهزة السيليكون. تعمل هذه النماذج مع معظم IDEs ومصححات البرامج المتوافقة مع معايير الصناعة ، وهي متوفرة من Imperas وشركاء توزيع Imperas EDA المعتمدين.

تعد الدقة والأداء وقابلية الاستخدام أمرًا بالغ الأهمية عندما يتعلق الأمر بنماذج محاكاة المعالج ، كما أن نماذج Imperas لمعالج SiFive IP عبارة عن عرض مبرمج تعليمي دقيق (IA) يمثل عرضًا للوظائف الكاملة لبروتوكول IP الأساسي ، بما في ذلك المستخدم ، والمميز ، والنظام ، و تصحيح الأخطاء ، بالإضافة إلى خيارات التكوين لملحقات المتجه RISC-V والتعليمات المخصصة.

هذه النماذج قادرة على تقديم أداء محاكاة من 100 إلى 1,000 ثانية من MIPS على كمبيوتر مضيف متواضع التكوين ؛ على سبيل المثال ، يقوم نموذج النظام الأساسي الافتراضي لـ SiFive Freedom U540 SoC المزود بخمس نوى من SiFive CPU بتشغيل SMP Linux في أقل من 10 ثوانٍ.

تقترن سهولة الاستخدام الكاملة لنماذج Imperas بأدوات التصحيح والتحليل Imperas التي تدعم مهام التصميم متعددة النواة، بما في ذلك نقل نظام التشغيل والتجريد لتطوير التطبيقات. بالإضافة إلى ذلك، جهاز محاكاة Imperas مع محاكاة تحويل التعليمات البرمجية الخاصة التكنلوجيا يمكن دمجها في بيئات EDA القياسية الأخرى مثل SystemC وSystemVerilog وأدوات المحاكاة/المحاكاة المعروفة من Cadence وSiemens EDA وSynopsys بالإضافة إلى العرض المستند إلى السحابة من Metrics Technologies.

يعد تصحيح أخطاء البرامج وتحليلها أمرًا بالغ الأهمية ، وتمكن أدوات Imperas المطورين من فحص الأنشطة عبر SoC متعدد النواة الكامل ، بما في ذلك التفاعلات عبر التسلسل الهرمي للتصميم للأجهزة الأساسية إلى الأساسية ومن الأساسية إلى الأجهزة الطرفية ، مع وصول فريد وتحكم باستخدام البرنامج ضمن التطوير بدون تعديل.

بشكل متزايد ، تعد وظائف البرامج جزءًا من شهادات النظام النهائي في التطبيقات عالية الموثوقية مثل السيارات ، و Mil-Aero ، و Medical ، و IoT الصناعي ، وأنظمة السلامة الحرجة الأخرى.

قال كريس جونز ، نائب رئيس تسويق المنتجات ، SiFive: "تعمل حريات التصميم الخاصة بـ RISC-V وامتدادات المتجهات على تغيير الحدود التقليدية بين مراحل البرامج والأجهزة في تطوير SoC". "تساعد نماذج Imperas الخاصة بنواة SiFive المطورين في الاستكشاف المعماري لشركة SoC عبر المرونة الكاملة لـ SiFive Core IP Portfolio ، وتدعم تطوير البرامج المبكرة ، وهو عامل حاسم في التحقق من صحة حلول الذكاء الاصطناعي الجديدة."

“كل مشاريع SoC تدور حول الشراكات. قال فيل دورسكي ، مدير التحالفات الاستراتيجية ، SiFive ، "يعمل مهندسو الأجهزة والبرمجيات معًا ، مع نظام بيئي كامل من المؤيدين". "من خلال تعاون Imperas هذا ، سيستفيد عملاؤنا المشتركون من توفر نماذج SiFive المؤهلة المتوافقة مع تدفقات أدوات EDA السائدة."

قال سيمون دافيدمان ، الرئيس التنفيذي لشركة Imperas Software: "تغطي محفظة SiFive Core IP طيف RISC-V ISA ، من وحدات التحكم المضمنة إلى المعالجات المتعددة التي تدعم SMP Linux ، بالإضافة إلى أحدث المسرعات القائمة على المتجهات". "هذه هي نقاط البداية للجيل التالي من الأجهزة الخاصة بالمجال عبر جميع قطاعات وتطبيقات السوق تقريبًا. Imperas جاهز لدعم التصميمات التي تتميز بنواة واحدة من خلال المصفوفات متعددة النواة باستخدام نماذج SiFive المؤهلة. "