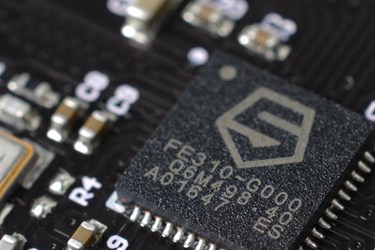

SiFive משתפת פעולה עם Imperas, מעניקה דוגמאות

תוכנת Imperas, מומחית בפלטפורמות וירטואליות והדמיית תוכנה עם ביצועים גבוהים, הודיעה כי SiFive, המובילה בתעשייה במעבדי RISC-V ופתרונות סיליקון, העפילה את דגמיה למגוון המלא של תיק ה- Core IP של מעבד ה- SiFive.

מודלים של סימולציה הם נקודת התחלה חיונית לחקר אדריכלי SoC מוקדם, שכן מעצבי מערכות משתמשים בפלטפורמות וירטואליות לבדיקת עומסי עבודה מלאים וערכות נתונים כדי לייעל תצורות מרובות ליבות.

ככל שתכנון ופיתוח החומרה מתקדמים על בסיס מתווה פונקציונלי זה, מודל הסימולציה הוא הבסיס התומך באבות טיפוס וירטואליים לפיתוח תוכנה מוקדם הרבה לפני שזמינים מכשירי סיליקון. מודלים אלה עובדים עם מרבית ה- IDEs והבאגים של התוכנה הסטנדרטיים בתעשייה, והם זמינים מ- Imperas ושותפי ההפצה של Imperas EDA שאושרו.

דיוק, ביצועים ושימושיות הם קריטיים בכל מה שקשור למודלים של סימולציית מעבדים והוא מודלים של Imperas עבור מעבד SiFive IP הם מתכנת הדרכה מדויק (IA) המציג ייצוג של הפונקציונליות המלאה של ה- IP הליבה, כולל מערכת, מערכת מיוחדת, ו מצבי איתור באגים, בתוספת אפשרויות התצורה של הרחבות הווקטור RISC-V והוראות מותאמות אישית.

מודלים אלה מסוגלים לספק ביצועי סימולציה של 100 עד 1,000 שניות של MIPS במחשב מארח מוגדר בצניעות; כדוגמה, מודל הפלטפורמה הווירטואלית של SiFive Freedom U540 SoC עם חמש ליבות מעבד SiFive מגביר את SMP Linux תוך פחות מ -10 שניות.

השימושיות המלאה של דגמי Imperas יחד עם כלי ניפוי באגים וניתוח Imperas התומכים במשימות עיצוב מרובות ליבות, כולל העברה של מערכת ההפעלה והפשטות לפיתוח יישומים. בנוסף, סימולטור Imperas עם הדמיית קוד-מורפינג קניינית טֶכנוֹלוֹגִיָה ניתן לשלב בתוך סביבות EDA סטנדרטיות אחרות כגון SystemC, SystemVerilog וכלי סימולציה/אמולציה ידועים מבית Cadence, Siemens EDA ו-Synopsys בתוספת ההצעה מבוססת הענן של Metrics Technologies.

איתור באגים וניתוחים של תוכנה הם קריטיים וכלי ה- Imperas מאפשרים למפתחים לבחון את הפעילויות ברחבי ה- SoC הרב-ליבתי המלא, כולל אינטראקציות בכל היררכיית העיצוב עבור ליבות ליבות וליבה-לציוד היקפי, עם גישה ובקרה ייחודיים באמצעות התוכנה הנמצאת תחת פיתוח ללא שינוי.

יותר ויותר, פונקציונליות תוכנה היא חלק מהסמכות המערכת הסופיות ביישומים אמינים במיוחד כמו רכב, Mil-Aero, Medical, IoT תעשייתי ומערכות קריטיות לבטיחות אחרות.

"חירויות העיצוב של RISC-V והרחבות וקטוריות משנות את הגבולות המסורתיים בין שלבי התוכנה והחומרה של פיתוח SoC", אמר כריס ג'ונס, סמנכ"ל שיווק מוצרים, SiFive. "דגמי Imperas של ליבות SiFive עוזרים למפתחים בחיפושי אדריכלות SoC על פני הגמישות המלאה של תיק ה- IP של SiFive, ותומכים בפיתוח תוכנה מוקדם, המהווה גורם קריטי באימות פתרונות AI חדשים."

"פרויקטים של SoC הם כולה שותפויות; מהנדסי חומרה ותוכנה עובדים יחד, עם מערכת אקולוגית מלאה של תומכים, "אמר פיל דבורסקי, מנהל הבריתות האסטרטגיות, SiFive. "בשיתוף פעולה זה של Imperas, הלקוחות המשותפים שלנו ייהנו מהזמינות של דגמים מוסמכים של SiFive התואמים לתזרים הכללי של EDA."

"תיק ה- SiFive Core IP מכסה את הספקטרום של ה- ISA של RISC-V, החל מבקרים משובצים, ועד למעבדים מרובי-תומכים ב- SMP Linux, בתוספת מאיצים מבוססי-וקטור אחרונים", אמר סיימון דייווידמן, מנכ"ל Imperas Software. "אלה נקודות ההתחלה לדור הבא של מכשירים ספציפיים לתחום כמעט בכל פלחי השוק והיישומים. Imperas מוכנה לתמוך בעיצובים הכוללים מערכי ליבה אחת עד לליבות רבות עם הדגמים המוסמכים שלנו של SiFive. "