SiFive colabora com Imperas, qualifica modelos

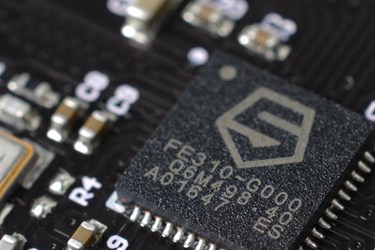

A Imperas Software, especialista em plataformas virtuais e simulação de software de alto desempenho, anunciou que a SiFive, líder da indústria em processadores RISC-V e soluções de silício, qualificou seus modelos para toda a gama de processadores SiFive Core IP Portfolio.

Os modelos de simulação são um ponto de partida essencial para a exploração da arquitetura de SoC inicial, pois os designers de sistemas usam plataformas virtuais para testar cargas de trabalho e conjuntos de dados completos de aplicativos para otimizar configurações de vários núcleos.

À medida que o design e o desenvolvimento de hardware progridem com base neste esboço funcional, o modelo de simulação é a base que dá suporte a protótipos virtuais para o desenvolvimento inicial de software muito antes que os dispositivos de silício estejam disponíveis. Esses modelos funcionam com a maioria dos IDEs e depuradores de software padrão da indústria e estão disponíveis na Imperas e em parceiros de distribuição aprovados da Imperas EDA.

Precisão, desempenho e usabilidade são críticos quando se trata de modelos de simulação de processador e os modelos Imperas para IP do processador SiFive são uma representação da visão do programador Preciso de Instrução (IA) da funcionalidade completa do IP principal, incluindo usuário, privilegiado, sistema e modos de depuração, além das opções de configuração para as extensões de vetor RISC-V e instruções personalizadas.

Esses modelos são capazes de fornecer desempenho de simulação de 100s a 1,000s de MIPS em um PC host com configuração modesta; como exemplo, o modelo de plataforma virtual do SoC SiFive Freedom U540 com cinco núcleos de CPU SiFive inicializa o SMP Linux em menos de 10 segundos.

A usabilidade total dos modelos Imperas é combinada com as ferramentas de depuração e análise Imperas que suportam tarefas de design multicore, incluindo portabilidade de sistema operacional e abstrações para desenvolvimento de aplicativos. Além disso, o simulador Imperas com simulação proprietária de code-morphing tecnologia pode ser integrado a outros ambientes EDA padrão, como SystemC, SystemVerilog e ferramentas de simulação/emulação conhecidas da Cadence, Siemens EDA e Synopsys, além da oferta baseada em nuvem da Metrics Technologies.

A depuração e análise de software são críticas e as ferramentas Imperas permitem aos desenvolvedores introspectar as atividades em todo o SoC multicore, incluindo interações em toda a hierarquia de design de núcleo a núcleo e núcleo a periféricos, com acesso e controle exclusivos usando o software em desenvolvimento sem modificação.

Cada vez mais, a funcionalidade do software faz parte das certificações do sistema final em aplicativos de alta confiabilidade, como Automotivo, Mil-Aero, Médico, IoT Industrial e outros sistemas críticos de segurança.

“As liberdades de design de RISC-V e extensões de vetor estão mudando os limites tradicionais entre as fases de software e hardware do desenvolvimento de SoC”, disse Chris Jones, vice-presidente de marketing de produto da SiFive. “Os modelos Imperas dos núcleos SiFive ajudam os desenvolvedores com a exploração arquitetônica de SoC em toda a flexibilidade do portfólio SiFive Core IP e oferecem suporte ao desenvolvimento inicial de software, que é um fator crítico na validação de novas soluções de IA.”

“Os projetos SoC são todos sobre parcerias; engenheiros de hardware e software trabalhando juntos, com um ecossistema completo de apoiadores ”, disse Phil Dworsky, Diretor, Alianças Estratégicas, SiFive. “Com esta colaboração da Imperas, nossos clientes mútuos se beneficiarão da disponibilidade de modelos qualificados de SiFive que são compatíveis com os fluxos de ferramentas EDA convencionais.”

“O portfólio SiFive Core IP cobre o espectro do RISC-V ISA, de controladores incorporados a multiprocessadores que suportam SMP Linux, além dos mais recentes aceleradores baseados em vetores”, disse Simon Davidmann, CEO da Imperas Software. “Esses são os pontos de partida para a próxima geração de dispositivos específicos de domínio em quase todos os segmentos de mercado e aplicativos. A Imperas está pronta para oferecer suporte a projetos com matrizes de núcleo único a muitos núcleos com nossos modelos qualificados de SiFive. ”