SiFive는 Imperas와 협력하여 모델을 검증합니다.

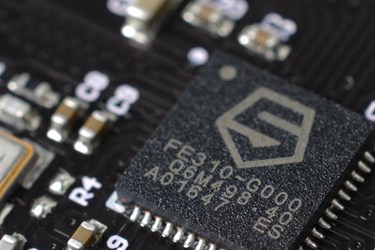

가상 플랫폼 및 고성능 소프트웨어 시뮬레이션 전문가 인 Imperas Software는 RISC-V 프로세서 및 실리콘 솔루션의 업계 리더 인 SiFive가 SiFive 프로세서 코어 IP 포트폴리오의 전체 범위에 대해 모델을 검증했다고 발표했습니다.

시뮬레이션 모델은 시스템 설계자가 가상 플랫폼을 사용하여 전체 애플리케이션 워크로드와 데이터 세트를 테스트하여 멀티 코어 구성을 최적화하기 때문에 초기 SoC 아키텍처 탐색을위한 필수 시작점입니다.

이 기능 개요를 기반으로 하드웨어 설계 및 개발이 진행됨에 따라 시뮬레이션 모델은 실리콘 장치를 사용할 수 있기 훨씬 전에 초기 소프트웨어 개발을위한 가상 프로토 타입을 지원하는 기반이됩니다. 이러한 모델은 대부분의 산업 표준 소프트웨어 IDE 및 디버거에서 작동하며 Imperas 및 승인 된 Imperas EDA 배포 파트너에서 제공됩니다.

프로세서 시뮬레이션 모델과 관련하여 정확성, 성능 및 사용성은 매우 중요하며 SiFive 프로세서 IP 용 Imperas 모델은 사용자, 권한, 시스템 및 사용자를 포함하여 코어 IP의 전체 기능에 대한 IA (Instruction Accurate) 프로그래머의 관점 표현입니다. 디버그 모드와 RISC-V 벡터 확장 및 사용자 지정 명령에 대한 구성 옵션.

이러한 모델은 적절하게 구성된 호스트 PC에서 100 ~ 1,000 개의 MIPS 시뮬레이션 성능을 제공 할 수 있습니다. 예를 들어 540 개의 SiFive CPU 코어가있는 SiFive Freedom U10 SoC의 가상 플랫폼 모델은 XNUMX 초 이내에 SMP Linux를 부팅합니다.

Imperas 모델의 완전한 유용성은 애플리케이션 개발을 위한 OS 포팅 및 추상화를 포함하여 멀티코어 설계 작업을 지원하는 Imperas 디버그 및 분석 도구와 결합됩니다. 또한 독점적인 코드 모핑 시뮬레이션을 갖춘 Imperas 시뮬레이터 technology SystemC, SystemVerilog, Cadence, Siemens EDA 및 Synopsys의 잘 알려진 시뮬레이션/에뮬레이션 도구와 Metrics Technologies의 클라우드 기반 제품과 같은 다른 표준 EDA 환경에 통합될 수 있습니다.

소프트웨어 디버그 및 분석이 중요하며, Imperas 도구를 사용하면 개발자가 아래의 소프트웨어를 사용하여 고유 한 액세스 및 제어를 통해 코어-코어 및 코어-주변 장치에 대한 설계 계층 구조 전반의 상호 작용을 포함하여 전체 멀티 코어 SoC에서 활동을 조사 할 수 있습니다. 수정없이 개발.

점차적으로 소프트웨어 기능은 자동차, 군사 항공, 의료, 산업용 IoT 및 기타 안전에 중요한 시스템과 같은 고 신뢰성 애플리케이션에서 최종 시스템 인증의 일부입니다.

SiFive의 제품 마케팅 부사장 인 Chris Jones는“RISC-V 및 벡터 확장의 설계 자유는 SoC 개발의 소프트웨어 및 하드웨어 단계 사이의 전통적인 경계를 바꾸고 있습니다. "SiFive 코어의 Imperas 모델은 개발자가 SiFive 코어 IP 포트폴리오의 완전한 유연성을 통해 SoC 아키텍처를 탐색하도록 돕고, 새로운 AI 솔루션을 검증하는 데 중요한 요소 인 초기 소프트웨어 개발을 지원합니다."

“SoC 프로젝트는 모두 파트너십에 관한 것입니다. 하드웨어 및 소프트웨어 엔지니어는 완전한 지지자 에코 시스템과 함께 협력합니다.”라고 SiFive의 전략적 제휴 담당 이사 인 Phil Dworsky는 말했습니다. "이 Imperas 협력을 통해 우리의 상호 고객은 주류 EDA 도구 흐름과 호환되는 SiFive 인증 모델을 이용할 수있는 혜택을 누릴 수 있습니다."

Imperas Software의 CEO 인 Simon Davidmann은“SiFive Core IP 포트폴리오는 임베디드 컨트롤러에서 SMP Linux를 지원하는 멀티 프로세서에 이르기까지 RISC-V ISA의 스펙트럼과 최신 벡터 기반 가속기를 포함합니다. “이것은 거의 모든 시장 부문과 애플리케이션에서 차세대 도메인 별 장치의 시작점입니다. Imperas는 SiFive 인증 모델을 사용하여 단일 코어에서 다중 코어 어레이에 이르는 설계를 지원할 준비가되어 있습니다.”